# DM3730/AM3703 Torpedo SOM Hardware Specification

Hardware Documentation

Logic PD // Products Published: June 2011 Last revised: March 2013

This document contains valuable proprietary and confidential information and the attached file contains source code, ideas, and techniques that are owned by Logic PD, Inc. (collectively "Logic PD's Proprietary Information"). Logic PD's Proprietary Information may not be used by or disclosed to any third party except under written license from Logic PD, Inc.

Logic PD, Inc. makes no representation or warranties of any nature or kind regarding Logic PD's Proprietary Information or any products offered by Logic PD, Inc. Logic PD's Proprietary Information is disclosed herein pursuant and subject to the terms and conditions of a duly executed license or agreement to purchase or lease equipment. The only warranties made by Logic PD, Inc., if any, with respect to any products described in this document are set forth in such license or agreement. Logic PD, Inc. shall have no liability of any kind, express or implied, arising out of the use of the Information in this document, including direct, indirect, special or consequential damages.

Logic PD, Inc. may have patents, patent applications, trademarks, copyrights, trade secrets, or other intellectual property rights pertaining to Logic PD's Proprietary Information and products described in this document (collectively "Logic PD's Intellectual Property"). Except as expressly provided in any written license or agreement from Logic PD, Inc., this document and the information contained therein does not create any license to Logic PD's Intellectual Property.

The Information contained herein is subject to change without notice. Revisions may be issued regarding changes and/or additions.

© Copyright 2013, Logic PD, Inc. All Rights Reserved.

# **Revision History**

| REV | EDITOR  | REVISION DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Schematic<br>PN & REV | APPROVAL | DATE     |

|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------|----------|

| 1   | NJK     | -Preliminary Release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1017879<br>Rev A      | JCA      | 06/23/11 |

| А   | SO, NJK | -Official Release; -Throughout: Removed preliminary markings; updated baseboard references to Torpedo Launcher 3; - Section 1.2: Added PRCM to list; -Section 1.4: Added reference to DM3730/AM3703 Torpedo SOM Thermal Management WP; -Section 2.3:2: Updated section to point to Torpedo SOM Mechanical Hold-Down Scenarios WP in place of Appendix B; -Table 2.3: Added note 3; -Table 3.2: Updated idle and suspend power numbers for DM3730 Android Gingerbread 2.3.4 BSP v1.2 and DM37x Linux BSP v2.1-0; added note 7; -Section 4.8: Added S-video to features list; -Section 5.2.1: Added important note; -Section 5.6: Changed section name to power supplies; added information regarding the availability of VIO_1V8 as a reference voltage; -Section 5.7.1: Added information about how T2_REGEN can be used to control power for external power ICs or LDOs; -Added Section 5.7.2; -Added Sections 5.8, 5.8.1, 5.8.2, 5.8.3, and 5.8.4; -Section 7.2: Added note 4 to pin out table; updated description for J2.17; corrected Ball BGA numbers for J2.95, J2.97, and J2.100; corrected function for J2.95 and J2.97; -Appendix A: Included updated mechanical drawing that includes connector pin orientations; -Removed Appendix B | 1017879<br>Rev A      | NJK, RAH | 08/06/12 |

| В   | SO, NJK | -Table 3.2: Updated idle and suspend power numbers for DM3730/AM3703 Android Gingerbread 2.3.4 BSP v1.4 and DM37x Linux BSP v2.3-2; -Section 4.6: Added note that proper USB adapter cable is necessary for USB 2.0 OTG to function as host; added link to Digi-Key adapter cable that supports host function; -Section 7: Added note regarding purpose of I/O column in pin description tables; -Section 7.1: Added processor pin for MCBSP3_DR (J1:77) to pinout table; -Section 7.2: Changed I/O column to input only for the non-default signals on J2:55, J2:57, J2:61, and J2:63; changed the I/O to output only for the non-default signals on J2:71; -Table Table 7.2: Changed I/O column to input only for the non-default signals on J2:55, J2:57, J2:61, and J2:63; changed the I/O to output only for the non-default signals on J2:65, J2:67, J2:69, and J2:71                                                                                                                                                                                                                                                                                                                                                                      | 1017879<br>Rev B      | BSB, RAH | 03/14/13 |

Please check the <u>Logic PD website</u><sup>1</sup> for the latest revision of this manual and other documentation.

\_

<sup>&</sup>lt;sup>1</sup> http://www.logicpd.com/

## **Table of Contents**

| 1 | Int        | roduction                                               |     |

|---|------------|---------------------------------------------------------|-----|

|   | 1.1        | Product Overview                                        | 1   |

|   | 1.2        | Abbreviations, Acronyms, & Definitions                  | 1   |

|   | 1.3        | Scope of Document                                       | 2   |

|   | 1.4        | Additional Documentation Resources                      | 2   |

| 2 | Fu         | nctional Specification                                  | 3   |

|   | 2.1        | Processor                                               |     |

|   | 2.1        |                                                         |     |

|   |            | I.2 AM3703 Processor Highlights                         |     |

|   | 2.2        | DM3730/AM3703 Torpedo SOM Interface                     | . 5 |

|   | 2.3        |                                                         |     |

|   |            | 3.1 DM3730/AM3703 Torpedo SOM Mechanical Drawings       | 7   |

|   |            | 3.2 Example DM3730/AM3703 Torpedo SOM Retention Methods |     |

|   | 2.4        | Temperature Specifications                              |     |

| 3 |            | ectrical Specification                                  |     |

| 4 |            | ripheral Specification                                  |     |

| _ | 4.1        | Clocks                                                  |     |

|   | 4.1        | Memory                                                  |     |

|   | 4.2        |                                                         |     |

|   | 4.2<br>4.2 |                                                         |     |

|   |            |                                                         |     |

|   | 4.3        | Audio Codec                                             |     |

|   | 4.4        | Display Interface                                       |     |

|   | 4.5        |                                                         |     |

|   | 4.5        |                                                         |     |

|   | 4.5        |                                                         |     |

|   | 4.5        |                                                         |     |

|   | 4.5        |                                                         |     |

|   | 4.5        |                                                         |     |

|   | 4          | 4.5.5.1 Reserved I2C Addresses                          |     |

|   | 4.6        | USB Interface                                           |     |

|   | 4.7        | General Purpose I/O                                     | 13  |

|   | 4.8        | Expansion/Feature Options                               |     |

| 5 | Sy         | stem Integration                                        | 14  |

|   | 5.1        | Configuration                                           | 14  |

|   | 5.2        | Resets                                                  | 14  |

|   | 5.2        | 2.1 Master Reset (MSTR_nRST)—Reset Input                | 14  |

|   | 5.2        |                                                         | 14  |

|   | 5.3        | Interrupts                                              |     |

|   | 5.4        | JTAG Debugger Interface                                 |     |

|   | 5.5        | ETM Adapter Interface                                   |     |

|   | 5.6        | Power Supplies                                          |     |

|   | 5.6        | • • • • • • • • • • • • • • • • • • • •                 |     |

|   | 5.6        |                                                         |     |

|   | 5.7        | System Power Management                                 |     |

|   | 5.7        | · ·                                                     |     |

|   | 5.7        |                                                         |     |

|   | 5.8        | Processor Power Management                              |     |

|   | 5.8        | P.1 Dynamia Voltaga and Eraguanay Scaling               | 10  |

|   |            | ,                                                       | 17  |

|   | 5.8        |                                                         |     |

|   | 5.8        | ,                                                       |     |

|   | 5.8        | 1 3                                                     |     |

|   | 5.9        | Boot Modes                                              |     |

| _ |            | ESD Considerations                                      |     |

| 6 | Me         | emory & I/O Mapping                                     | 19  |

#### DM3730/AM3703 Torpedo SOM Hardware Specification

| 7 | Pin | Descriptions & Functions          | 20 |

|---|-----|-----------------------------------|----|

|   |     | J1 Connector 100-Pin Descriptions |    |

|   |     | J2 Connector 100-Pin Descriptions |    |

|   |     | Configurable Pins                 |    |

|   |     | dix A: Mechanical Drawings        |    |

# **Table of Figures**

| Figure 2.1: DM3730 Processor Block Diagram          | 4  |

|-----------------------------------------------------|----|

| Figure 2.2: AM3703 Processor Block Diagram          | 5  |

| Figure 2.3: DM3730/AM3703 Torpedo SOM Block Diagram | 6  |

|                                                     |    |

| Table of Tables                                     |    |

| Table 2.1: Mechanical Characteristics of SOM        | 6  |

| Table 2.2: Baseboard Mating Connectors              | 7  |

| Table 2.3: Temperature Characteristics of SOM       | 7  |

| Table 3.1: Absolute Maximum Ratings                 | 8  |

| Table 3.2: Recommended Operating Conditions         | 8  |

| Table 4.1: Processor Clock Specifications           | 10 |

| Table 5.1: Signals for Multiple Boot Sources        | 18 |

| Table 6.1: Chip Select Signals                      | 19 |

| Table 7.1: Feature Gain/Loss through Customization  | 35 |

| Table 7.2: Configurable J1 and J2 Connector Pins    | 36 |

#### 1 Introduction

#### 1.1 Product Overview

The DM3730/AM3703 Torpedo System on Module (SOM) is an ultra-compact form factor based on Texas Instruments' DaVinci™ DM3730 and Sitara™ AM3703 processors.

The DM3730/AM3703 Torpedo SOM occupies less than one square inch, but boasts PC-like speeds up to 1 GHz with long battery life. Partnered with such high performance is a startlingly low power consumption of less than 5 mW when in suspend state. This balance of speed and power is accomplished through Logic PD's vast system design experience; understanding the most detailed workings of each component and their interaction with one another creates a product that operates at optimal efficiency.

By remaining footprint compatible with Logic PD's existing OMAP35x Torpedo SOM, the DM3730/AM3703 Torpedo SOM extends the roadmaps of existing products and provides an upgrade path from today's products to future technologies.

The ultra-compact DM3730/AM3703 Torpedo SOM is an ideal off-the-shelf solution for applications in markets where space is a premium. From point-of-care medical devices to handheld radios to mobile Internet devices, the DM3730/AM3703 Torpedo SOM allows for the powerful versatility and compact designs needed in today's market-changing products.

The Zoom™ DM3730 Torpedo Development Kit includes all of the necessary accessories to immediately begin development, helping customers deliver their products to market sooner.

#### 1.2 Abbreviations, Acronyms, & Definitions

| ADC | Analog to Digital Converter |

|-----|-----------------------------|

| BSP | Board Support Package       |

| DTD | D 14 B                      |

BTB Board-to-Board

DDR Double Data Rate (RAM)

DMA Direct Memory Access

ESD Electrostatic Discharge

FIFO First In First Out

GPIO General Purpose Input Output

GPMC General Purpose Memory Controller

GPO General Purpose Output I2C Inter-Integrated Circuit

I2S Inter-Integrated Circuit Sound

IC Integrated Circuit

I/O Input/Output

IRQ Interrupt Request

LCD Liquid Crystal Display

LDO Low Dropout (Regulator)

McBSP Multi-channel Buffered Serial Port

OTG On-the-Go (USB)

PCB Printed Circuit Board

PCMCIA Personal Computer Memory Card International Association (PC Cards)

PHY Physical Layer

PLL Phase Lock Loop

PoP Package on Package

PRCM Power Reset Clock Manager

PWM Pulse Width Modulation

RTC Real Time Clock

SDIO Secure Digital Input Output

SDRAM Synchronous Dynamic Random Access Memory

SOM System on Module SSP Synchronous Serial Port

SPI Standard Programming Interface STN Super-Twisted Nematic (LCD) TFT Thin Film Transistor (LCD)

TI Texas Instruments

TSC Touch Screen Controller

TTL Transistor-Transistor Logic

UART Universal Asynchronous Receive Transmit

#### 1.3 Scope of Document

This hardware specification is unique to the design and use of the DM3730/AM3703 Torpedo SOM as designed by Logic PD and does not intend to include information outside of that scope. Detailed information about the Texas Instruments (TI) DM3730/AM3703 processors or any other device component on the SOM can be found in their respective manuals and specification documents. Please see Section 1.4 for additional resources.

#### 1.4 Additional Documentation Resources

The following documents or documentation resources are referenced within this hardware specification.

- TI's DM3730, DM3725 Digital Media Processors Datasheet<sup>2</sup>

- Tl's AM3715, AM3703 Sitara ARM Microprocessors Datasheet<sup>3</sup>

- TI's AM/DM37x Multimedia Device Technical Reference Manual (TRM)²

- Tl's TPS65950 Data Manual<sup>4</sup>

- TI's TPS65950 OMAP Power Management and System Companion Device TRM

- USB 2.0 Specification, <u>available from USB.org</u><sup>5</sup>

- Logic PD's Design Files (BOM, Schematic, and Layout) for all boards included in the development kit (baseboard, SOM, LCD), as well as all standard configuration SOMs. Sign into your account on Logic PD's website to access the files.

- Logic PD's WP 491 DM3730/AM3703 Torpedo SOM Thermal Management<sup>6</sup>

- Logic PD's LogicLoader v2.5 User Guide

- Logic PD's WP 419 Torpedo SOM Mechanical Hold-Down Scenarios<sup>8</sup>

<sup>&</sup>lt;sup>2</sup> http://focus.ti.com/docs/prod/folders/print/dm3730.html#technicaldocuments

<sup>&</sup>lt;sup>3</sup> http://focus.ti.com/docs/prod/folders/print/am3703.html#technicaldocuments

<sup>4</sup> http://focus.ti.com/docs/prod/folders/print/tps65950.html#technicaldocuments

http://www.usb.org/developers/docs/

http://support.logicpd.com/downloads/1522/

<sup>&</sup>lt;sup>7</sup> http://support.logicpd.com/downloads/1428/

http://support.logicpd.com/downloads/1279/

## 2 Functional Specification

#### 2.1 Processor

The Torpedo SOM uses TI's DaVinci™ DM3730 and Sitara™ AM3703 processors. The DM3730 is viewed as the superset configuration; the AM3703 does not include a DSP core or graphics accelerator.

#### 2.1.1 DM3730 Processor Highlights

This list comes from Tl's <u>DM3730 Digital Media Processor webpage</u>. <sup>9</sup> See Tl documentation for more details.

- Compatible with OMAP™ 3 Architecture

- ARM® microprocessor (MPU) Subsystem

- □ Up to 1-GHz ARM® Cortex<sup>TM</sup>-A8 Core, Also supports 300, 600, and 800-MHz

- □ NEON SIMD Coprocessor

- High Performance Image, Video, Audio (IVA2.2<sup>TM</sup>) Accelerator Subsystem

- □ Up to 800-MHz TMS320C64x+™ DSP Core

- Enhanced Direct Memory Access (EDMA) Controller (128 Independent Channels)

- □ Video Hardware Accelerators

- POWER SGX<sup>TM</sup> Graphics Accelerator (DM3730 only)

- □ Tile Based Acrchitecture Delivering up to 20 MPoly/sec

- Universal Scalable Shader Engine: Multi-threaded Engine Incorporating Pixel and Vertex Shader Functionality

- □ Industry Standard API Support: OpenGLES 1.1 and 2.0, OpenVG1.0

- □ Fine Grained Task Switching, Load Balancing, and Power Management

- Programmable High Quality Image Anti-Aliasing

- Advanced Very-Long-Instruction-Word (VLIW) TMS320C64x+<sup>TM</sup> DSP Core

- Eight Highly Independent Functional Units

- Six ALUs (32-/40-Bit); Each Supports Single 32- bit, Dual 16-bit, or Quad 8-bit, Arithmetic per Clock Cycle

- Two Multipliers Support Four 16 x 16-Bit Multiplies (32-Bit Results) per Clock Cycle or Eight 8 x 8-bit Multiplies (16-Bit Results) per Clock Cycle

- □ Load-Store Architecture With Non-Aligned Support

-

<sup>&</sup>lt;sup>9</sup> http://focus.ti.com/docs/prod/folders/print/dm3730.html

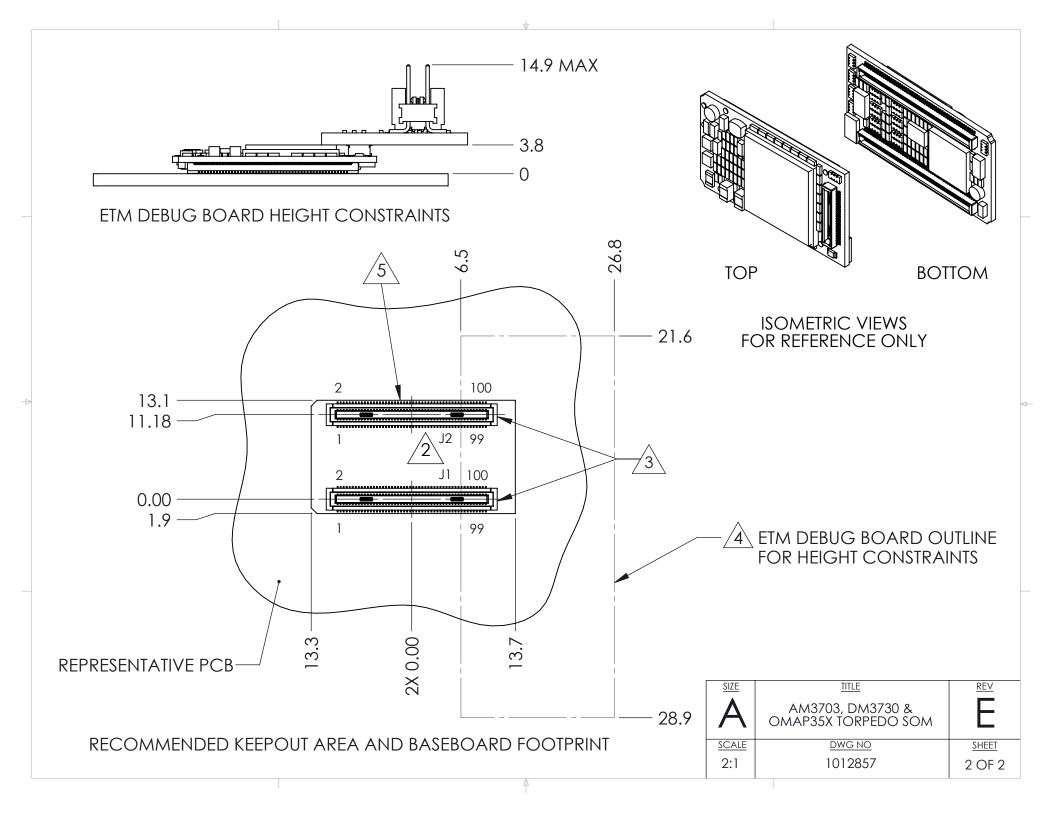

Figure 2.1: DM3730 Processor Block Diagram

**NOTE:** The block diagram pictured above comes from Tl's *DM3730*, *DM3725 Digital Media Processors Datasheet* (Literature Number: SPRS685D).

#### 2.1.2 AM3703 Processor Highlights

This list comes from TI's <u>AM3703 Digital Media Processor webpage</u>. <sup>10</sup> See TI documentation for more details.

- Compatible to OMAP™ 3 Architecture

- MPU Subsystem

- □ Up to 1-GHz Sitara<sup>™</sup> ARM® Cortex<sup>™</sup>-A8 Core Also supports 300, 600, and 800-MHz operation

- NEON SIMD Coprocessor

<sup>&</sup>lt;sup>10</sup> http://focus.ti.com/docs/prod/folders/print/am3703.html

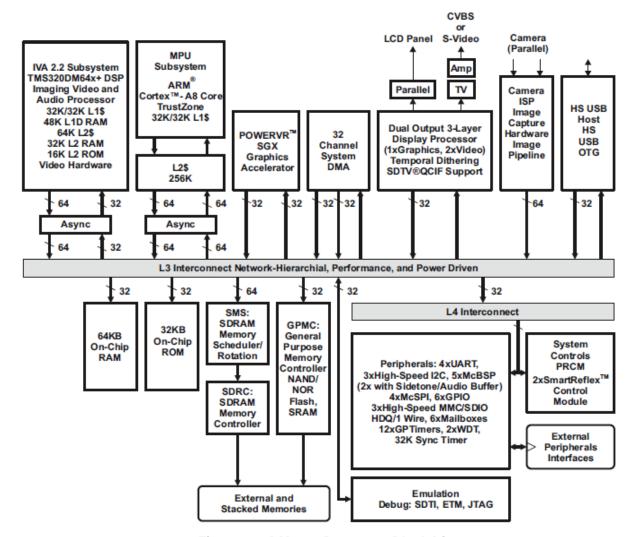

Figure 2.2: AM3703 Processor Block Diagram

**NOTE:** The block diagram pictured above comes from TI's *AM3715, AM3703 Sitara ARM Microprocessors Datasheet* (Literature Number: SPRS616F).

#### 2.2 DM3730/AM3703 Torpedo SOM Interface

Logic PD's common Torpedo SOM interface allows for easy migration to new processors and technology. Logic PD is constantly researching and developing new technologies to improve performance, lower cost, and increase feature capabilities. By using the common Torpedo SOM footprint, it may be possible to take advantage of Logic PD's work without having to re-spin the old design.

In fact, encapsulating a significant amount of your design onto the Torpedo SOM reduces any long-term risk of obsolescence. If a component on the Torpedo SOM design becomes obsolete, Logic PD will design for an alternative part that is transparent to your product. Furthermore, Logic

PD tests all SOMs prior to delivery, decreasing time-to-market and ensuring a simpler and less costly manufacturing process. Contact Logic PD 11 for more information.

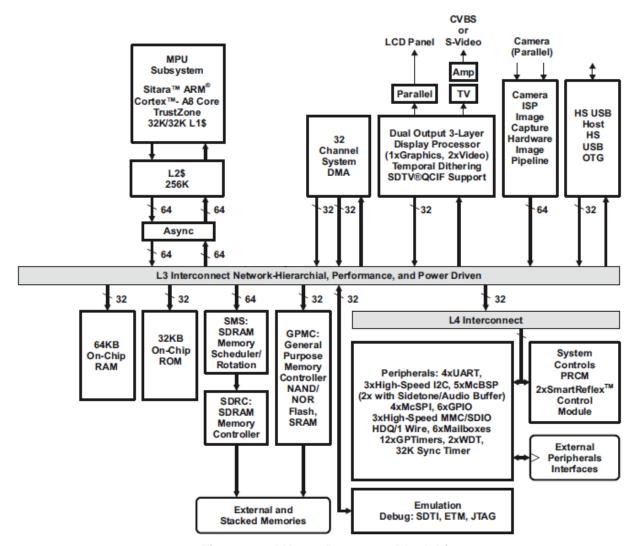

Figure 2.3: DM3730/AM3703 Torpedo SOM Block Diagram

#### 2.3 Mechanical Specifications

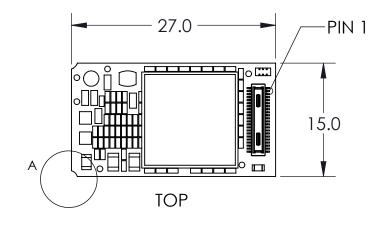

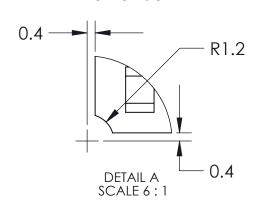

Table 2.1: Mechanical Characteristics of SOM

| Parameter                   | Min | Typical           | Max | Unit   | Notes |

|-----------------------------|-----|-------------------|-----|--------|-------|

| Dimensions                  | _   | 15.0 x 27.0 x 3.8 | _   | mm     | _     |

| Weight                      | _   | 1.96              | _   | Grams  | 1     |

| Connector Insertion/Removal | _   | 30                | _   | Cycles | _     |

#### **TABLE NOTES:**

1. May vary depending on SOM configuration.

\_

<sup>&</sup>lt;sup>11</sup> http://support.logicpd.com/support/askaquestion.php

The DM3730/AM3703 Torpedo SOM connects to a PCB baseboard through two 100-pin board-to-board (BTB) socket connectors.

Table 2.2: Baseboard Mating Connectors

| Ref Designator | Manufacturer | Torpedo Connector P/N | Mating Connector P/N |

|----------------|--------------|-----------------------|----------------------|

| J1, J2         | Hirose       | DF40C-100DP-0.4V(51)  | DF40C-100DS-0.4V(51) |

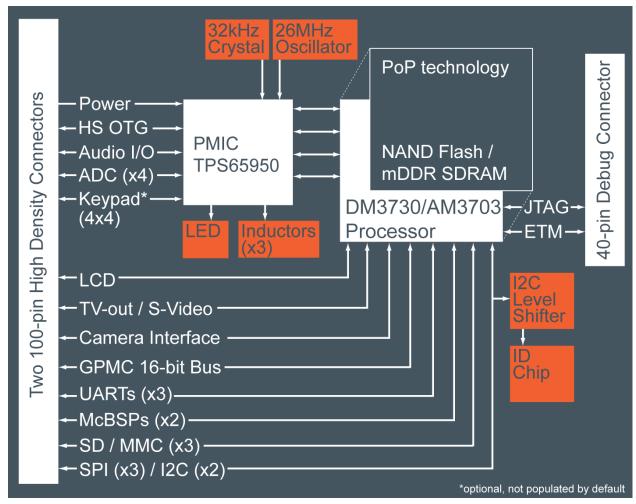

#### 2.3.1 DM3730/AM3703 Torpedo SOM Mechanical Drawings

Please see Appendix A for mechanical drawings of the DM3730/AM3703 Torpedo SOM and recommended baseboard footprint layout.

#### 2.3.2 Example DM3730/AM3703 Torpedo SOM Retention Methods

Logic PD has developed several methods to secure the DM3730/AM3703 Torpedo SOM in an end product. For mechanical drawings of these example retention methods, please see the WP 419 Torpedo SOM Mechanical Hold-Down Scenarios.

#### 2.4 Temperature Specifications

Table 2.3: Temperature Characteristics of SOM

| Parameter                        | Min | Typical | Max | Unit | Notes |

|----------------------------------|-----|---------|-----|------|-------|

| Commercial Operating Temperature | 0   | 25      | 70  | °C   | 1     |

| Industrial Operating Temperature | -40 | 25      | 85  | °C   | 2, 3  |

| Storage Temperature              | -40 | 25      | 85  | °C   | _     |

#### **TABLE NOTES:**

- 1. Junction temperature of the DM3730/AM3703 processor must stay below 90°C.

- 2. Junction temperature of the DM3730/AM3703 processor must stay below 105°C.

- Junction temperature of the DM3730/AM3703 processor must stay below 90°C in OPP130 or OPP1G.

## 3 Electrical Specification

Table 3.1: Absolute Maximum Ratings

| Parameter                     | Symbol       | Rating     | Unit |

|-------------------------------|--------------|------------|------|

| DC Main Battery Input Voltage | MAIN_BATTERY | 0.0 to 4.5 | V    |

| DC USB1_VBUS Input Voltage    | USB1_VBUS    | 0.0 to 7.0 | V    |

| RTC Backup Battery Voltage    | BACKUP_BATT  | 0.0 to 3.3 | V    |

**NOTE:** These stress ratings are only for transient conditions. Operation at, or beyond, absolute maximum rating conditions may affect reliability and cause permanent damage to the DM3730/AM3703 Torpedo SOM and its components.

**Table 3.2: Recommended Operating Conditions**

| Parameter                                 | Min          | Typical | Max         | Unit | Notes |

|-------------------------------------------|--------------|---------|-------------|------|-------|

|                                           | 2.7*         |         |             |      |       |

| DC Main Battery Input Voltage             | (see note 5) | 3.3     | 4.5         | V    | 5     |

| DC Main Battery Idle Power,<br>Android    | _            | 245.5   | _           | mW   | 2     |

| DC Main Battery Idle Power,<br>Linux      | _            | 245.5   | _           | mW   | 3     |

| DC Main Battery Suspend Power,<br>Android | _            | 8.7     | _           | mW   | 2,7   |

| DC Main Battery Suspend Power,<br>Linux   | _            | 6.2     | _           | mW   | 3,7   |

| DC USB1_VBUS Input Voltage                | 4.4          | 5.0     | 7.0         | V    | _     |

| DC RTC Backup Battery Voltage             | 1.8          | 3.2     | 3.3         | V    | _     |

| Input Signal High Voltage                 | 0.65 x VREF  | _       | VREF        | V    | 4, 6  |

| Input Signal Low Voltage                  | -0.3         | _       | 0.35 x VREF | V    | 4, 6  |

| Output Signal High Voltage                | VREF - 0.2   | _       | VREF        | V    | 4, 6  |

| Output Signal Low Voltage                 | GND          |         | 0.2         | V    | 6     |

#### **TABLE NOTES:**

- 1. General note: CPU power rails are sequenced on the SOM.

- 2. Running the DM3730/AM3703 Android Gingerbread 2.3.4 BSP v1.4 on the standard DM3730 Torpedo SOM configuration included in the Zoom DM3730 Torpedo Development Kit. Idle power was measured at the home screen after a fresh boot. Suspend power was measured after pressing the S2 button to enter suspend. Wattson<sup>TM</sup>, Logic PD's power measurement and performance monitoring application, was used to record all numbers.

- 3. Running the DM37x Linux BSP v2.3-2 on the standard DM3730 Torpedo SOM configuration included in the Zoom DM3730 Torpedo Development Kit. Idle power was measured at the home screen after a fresh boot. Suspend power was measured after pressing the S2 button to enter suspend. Wattson<sup>TM</sup>, Logic PD's power measurement and performance monitoring application, was used to record all numbers.

- 4. VREF represents the peripheral I/O supply reference for the specific CPU voltage rail.

- 5. 2.7V is the minimum threshold for the battery at which the device will turn OFF. However, the minimum voltage at which the device will power ON (if PWRON does not have a switch and is connected to MAIN\_BATTERY) is 3.2V ±100mV, assuming battery plug-in as the device switch on event. If PWRON has a switch then 3.2V is the minimum for the device to turn ON.

- 6. The exact minimum and maximum values depend on the specific pin being referenced. Please refer to Tl's *DM3730*, *DM3725 Digital Media Processors Datasheet* and *TPS65950 Data Manual* for exact values.

- 7. Suspend power numbers were taken with the versions of Logic PD's BSPs noted above in notes 2 and 3. Logic PD is continually improving the suspend power consumption through software updates. Logic PD's BSPs are also written for general use cases; the BSP may be further customized to offer lower suspend power numbers. Please <a href="contact Logic PD">contact Logic PD</a> for more information on low-power software offerings.

## 4 Peripheral Specification

#### 4.1 Clocks

The DM3730/AM3703 processors require an oscillator and crystal to enable proper internal timing. A 26.000 MHz oscillator is used to generate many of the processor's internal clocks via a series of Phase Lock Loops (PLLs) and signal dividers. To generate the core CPU clock, the 26.000 MHz signal is run through a Digital PLL controlled by the PRCM registers. Divisors are used to divide down the internal bus frequency to set the LCD, memory controller, camera interface, etc.

**IMPORTANT NOTE:** Please see TI's *AM/DM37x TRM* for additional information about processor clocking.

The second required crystal runs at 32.768 kHz and is connected directly to the TPS65950 PMIC. The 32.768 kHz clock is used for PMIC and CPU start-up and as a reference clock for the Real Time Clock (RTC) Module.

The CPU's microcontroller core clock speed is initialized by software on the DM3730/AM3703 Torpedo SOM. The SDRAM bus speed is set at 200 MHz in LogicLoader. Other clock speeds, such as core speed and specific serial baud rates, can be supported and modified in software for specific user applications.

The DM3730/AM3703 Torpedo SOM provides an external bus clock, uP\_BUS\_CLK. This clock is driven by the GPMC\_CLK pin.

| DM3730/AM3703<br>Processor Signal Name | DM3730/AM3703<br>Torpedo SOM Net Name | Default Software Value in LogicLoader |  |

|----------------------------------------|---------------------------------------|---------------------------------------|--|

| CORE                                   | N/A                                   | Up to 1 GHz                           |  |

| SDRC_CLK                               | N/A                                   | 200 MHz                               |  |

| GPMC_CLK                               | uP_BUS_CLK                            | Not configured                        |  |

Table 4.1: Processor Clock Specifications

#### 4.2 Memory

#### 4.2.1 Package on Package Memory (Mobile DDR and NAND)

The DM3730/AM3703 processors use Package-on-Package (PoP) technology to stack BGA memory devices on top of the CPU BGA. The processors use a 32-bit memory bus to interface to mobile DDR (mDDR) SDRAM and a 16-bit memory bus to interface to NAND.

Logic PD's default memory configuration on the DM3730/AM3703 Torpedo SOM is 256 MB mDDR and 512 MB NAND.

#### 4.2.2 External Memory

It is possible to expand the system's non-volatile storage capability by adding external flash ICs, SD memory, CompactFlash, or NAND flash. Please contact Logic PD for other possible peripheral designs.

#### 4.3 Audio Codec

The DM3730/AM3703 processors have multiple Multi-channel Buffered Serial Port (McBSP) interfaces that support PCM and I2S formats. Both PCM and I2S serial paths drive the built-in TPS65950 audio codec. From the TPS65950 PMIC, the outputs are CODEC\_OUTL and CODEC\_OUTR; these signals are available from the expansion connectors.

The codec in the TPS65950 PMIC performs up to full-duplex codec functions and supports variable sample rates from 8–96k samples per second. See the "Audio" chapter in TI's TPS65950 OMAP Power Management and System Companion Device TRM for more information.

**NOTE:** The DM3730/AM3703 Torpedo SOM also offers alternate serial interfaces for other codec devices. If you are looking for a different codec option, Logic PD has previously interfaced different high-performance audio codecs into other SOMs. Contact Logic PD for assistance in selecting an appropriate audio codec for your application.

#### 4.4 Display Interface

The DM3730/AM3703 processors have a built-in LCD controller supporting STN, color STN, and TFT panels at a resolution of up to HD 720p, 1280 x 720 x 24-bit color. See TI's AM/DM37x Multimedia Device TRM for additional information on the integrated LCD controller.

The signals from the DM3730/AM3703 LCD controller are organized by bit and color and can be interfaced through the SOM J1 and J2 connectors (see Section 7). Logic PD has written drivers for panels of different types and sizes. Please contact Logic PD before selecting a panel for your application.

**IMPORTANT NOTE:** Using the internal graphics controller will affect processor performance. Selecting display resolutions and color bits per pixel will vary processor busload.

#### 4.5 Serial Interfaces

The DM3730/AM3703 Torpedo SOM comes with the following serial channels: UARTA, UARTB, UARTC, three SPI ports, two MCBSP, and two I2C ports. If additional serial channels are required, please contact Logic PD for reference designs. Please see TI's AM/DM37x Multimedia Device TRM for additional information regarding serial communications.

#### 4.5.1 **UARTA**

UARTA has been configured as the main DM3730/AM3703 Torpedo SOM serial port based on the processor UART1. It is an asynchronous 16C750-compatible UART. This UART provides a high-speed serial interface that uses 64 byte First In / First Out (FIFO) and is capable of sending

and receiving serial data simultaneously. The signals from the DM3730/AM3703 Torpedo SOM are 1.8V Transistor-Transistor Logic (TTL) level signals, not RS232 level signals. The end-product design must provide an external RS232 transceiver for RS232 applications. Logic PD has provided an example reference design in the *Torpedo Launcher 3 Baseboard Schematics*. When choosing an RS232 transceiver, the designer should keep in mind cost, availability, ESD protection, and data rates.

The UARTA baud rate is set to a default 115.2 Kbits/sec, though it supports most common serial baud rates.

#### 4.5.2 UARTB

Serial Port UARTB (processor UART3) is an asynchronous 16C750-compatible UART. This UART is a high-speed serial interface that uses FIFO and is capable of sending and receiving serial data simultaneously. The signals from the DM3730/AM3703 Torpedo SOM are 1.8V TTL level signals, not RS232 level signals. The UARTB baud rate can also be set to most common serial baud rates.

#### 4.5.3 **UARTC**

Serial port UARTC (processor UART2) is an asynchronous 16C750-compatible UART. This UART is a high-speed serial interface that uses FIFO and is capable of sending and receiving serial data simultaneously. The signals from the DM3730/AM3703 Torpedo SOM are 1.8V TTL level signals, not RS232 level signals. The UARTC baud rate can also be set to most common serial baud rates.

#### 4.5.4 McSPI

The DM3730/AM3703 Torpedo SOM provides three external SPI ports with multiple chip selects. Additional SPI ports are available through different resistor populations. Please see Table 7.1 for more information.

#### 4.5.5 I2C

The DM3730/AM3703 Torpedo SOM supports two dedicated external I2C ports. The clock and data signals for the I2C2 and I2C3 ports have 4.7K ohm pull-up resistors. Please see TI's *AM/DM37x Multimedia Device TRM* for additional information.

#### 4.5.5.1 Reserved I2C Addresses

The DM3730/AM3703 Torpedo SOM contains a product ID chip that connects to the I2C bus. Logic PD software uses this product ID chip to determine hardware version information. As a result, the 7-bit I2C addresses listed below are used by the product ID chip and must be avoided in custom designs:

- **101 1000**

- **101 1001**

- **101 1010**

- **101 1011**

- **101 1100**

- **101 1101**

#### 4.6 USB Interface

The DM3730/AM3703 Torpedo SOM supports one USB 2.0 OTG port, which can function as a host or device/client. In order to for the port to operate as a host, a proper adapter cable must be used; Logic PD recommends one similar to the USB adapter cable by <u>Digi-Key</u><sup>12</sup> (part number 10-00003-ND).

The port can operate at up to 480 Mbit/sec. The USB controller for the OTG port is internal to the processor; an external PHY built into the TPS65950 PMIC supports the OTG port. For more information on using the OTG interfaces, please see Tl's *AM/DM37x Multimedia Device TRM*.

**IMPORTANT NOTE:** In order to correctly implement USB on the DM3730/AM3703 Torpedo SOM, additional impedance matching circuitry may be required on the USB1\_D+ and USB1\_D-signals before they can be used. USB 2.0 requirements specify the signals must be routed as differential pairs with 90 ohm differential impedance. Refer to the *USB 2.0 Specification* for detailed information.

#### 4.7 General Purpose I/O

Logic PD designed the DM3730/AM3703 Torpedo SOM to be flexible and provide multiple options for analog and digital GPIO. There are numerous digital GPIO pins on the DM3730/AM3703 Torpedo SOM that interface to the DM3730/AM3703 processor and TPS65950 PMIC; please see Section 7 for more information. If certain peripherals are not desired, such as the LCD controller, chip selects, IRQs, or UARTs, then more GPIO pins become available.

**DESIGN NOTE**: Due to buffer strength, an external serial resistor must be connected to the BGA balls where GPIO\_120 through GPIO\_127 and GPIO\_129 are muxed with MMC/SIM signals. See "Section 25.2" in TI's *DM3730*, *DM3725 Digital Media Processors TRM* (Literature Number: SPRUGN4K) for additional information.

#### 4.8 Expansion/Feature Options

The DM3730/AM3703 Torpedo SOM was designed for expansion and a variable feature set, providing all the necessary control signals and bus signals to expand the user's design. It is possible for a user to expand the DM3730/AM3703 Torpedo SOM's functionality even further by adding host bus devices. Some features that are implemented on the DM3730/AM3703 processors, but are not discussed herein, include: RTC, pulse width modulation (PWM), Secure Digital, MMC cards, SDIO cards, graphics accelerator, DSP codecs, Image Processing Unit, S-video, 1-wire interface, and the debug module. See TI's AM/DM37x Multimedia Device TRM and Logic PD's DM3730/AM3703 Torpedo SOM Schematics for more details. Logic PD has experience implementing additional options, including other audio codecs, Ethernet ICs, co-processors, and components on SOMs. Please contact Logic PD for potential reference designs before selecting your peripherals.

.

<sup>12</sup> http://www.digikey.com/scripts/DkSearch/dksus.dll?WT.z\_header=search\_go&lang=en&keywords=10-00003-ND&x=0&v=0&cur=USD

## 5 System Integration

#### 5.1 Configuration

The DM3730/AM3703 Torpedo SOM was designed to meet multiple applications for users with specific design and budget requirements. As a result, this DM3730/AM3703 Torpedo SOM supports a variety of embedded operating systems and hardware configurations. Please <a href="contact-Logic PD">contact-Logic PD</a> if you have additional hardware configurations to meet your specific application needs.

#### 5.2 Resets

The DM3730/AM3703 Torpedo SOM has a reset input (MSTR\_nRST) and a reset output (SYS\_nRESWARM). External devices can drive MSTR\_nRST low to assert reset to the product. The DM3730/AM3703 Torpedo SOM uses SYS\_nRESWARM to indicate to other devices that the DM3730/AM3703 Torpedo SOM is in reset.

#### 5.2.1 Master Reset (MSTR\_nRST)—Reset Input

Logic PD suggests that custom designs implementing the DM3730/AM3703 Torpedo SOM use the MSTR\_nRST signal as the "pin-hole" reset used in commercial embedded systems. The MSTR\_nRST triggers a power-on reset event in the processor and resets the entire CPU.

A low pulse on the MSTR\_nRST signal, asserted by an external source (for example, the reset button on the custom design application), will bring MSTR\_nRST low until the assertion source is de-asserted. There is no delay beyond the de-assertion of the external MSTR\_nRST signal source, so the custom design must ensure that the assertion time is sufficient for all related peripherals.

Logic PD suggests that for any external assertion source that triggers the MSTR\_nRST signal, analog or digital, de-bouncing should be used to generate a clean, one-shot reset signal.

**IMPORTANT NOTE:** MSTR\_nRST does not reset the TPS65950 PMIC; the TPS65950 is only reset by removing power from the SOM. Any custom reset circuit design should guard against the assertion of the reset lines during a low-power state. This is because some of the critical system power rails may have been turned off in the TPS65950 when entering the low-power state; toggling the MSTR\_nRST line will reset the processor, but not the TPS65950, leaving some of the critical system power rails off.

#### 5.2.2 DM3730/AM3703 Torpedo SOM Reset (SYS\_nRESWARM)—Reset output

All hardware peripherals should connect their hardware-reset pin to the SYS\_nRESWARM signal on the SOM's J2 connector. Internally, all DM3730/AM3703 Torpedo SOM peripheral hardware reset pins are connected to the SYS\_nRESWARM net.

#### 5.3 Interrupts

The DM3730/AM3703 processors incorporate the ARM Cortex-A8 interrupt controller which provides many inter-system interrupt sources and destinations. Most external GPIO signals can also be configured as interrupt inputs by configuring their pin control registers. Logic PD BSPs setup and process all onboard system and external DM3730/AM3703 Torpedo SOM interrupt sources. Refer to TI's *AM/DM37x Multimedia Device TRM* for additional information on using interrupts.

#### 5.4 JTAG Debugger Interface

The JTAG connection to the DM3730/AM3703 Torpedo SOM allows recovery of corrupted flash memory, real-time application debug, and DSP development (on the DM3730 processor). There are several third-party JTAG debuggers available for TI microcontrollers. The following signals make up the JTAG interface to the DM3730/AM3703 processor: TDI, TMS, TCK, TDO, nTRST, RTCK, EMU0, and EMU1. These signals are routed to reference designator J5 on the SOM.

**IMPORTANT NOTE:** When laying out the 20-pin connector, realize that it may not be numbered as a standard 20-pin 0.1" insulation displacement connector (IDC) through-hole connector. See the ETM Adapter Board reference design for further details. Each JTAG tool vendor may define the 20-pin IDC connector pin-out differently.

#### 5.5 ETM Adapter Interface

The Embedded Trace Macrocell (ETM) interface signals are available through connector J5 on the DM3730/AM3703 Torpedo SOM. Logic PD developed an adapter board—included with the Zoom DM3730 Torpedo Development Kit—that converts the available signals on J5 to the standard Mictor connector interface used by most common third-party ETM tool providers. The connector supports ETM\_D[15:0], ETM\_CLK, ETM\_CTL, and the JTAG signals listed in Section 5.4.

#### 5.6 Power Supplies

In order to ensure a flexible design, the DM3730/AM3703 Torpedo SOM has the following power areas: MAIN\_BATTERY and BACKUP\_BATT. All power areas are inputs to the DM3730/AM3703 Torpedo SOM. The module also provides VIO\_1V8 as a reference voltage. It may be used to supply up to 200 mA of power, although using an external supply is recommended.

#### 5.6.1 MAIN\_BATTERY

The MAIN\_BATTERY input is the main source of power for the DM3730/AM3703 Torpedo SOM. This input expects a voltage within typical single lithium-ion battery limits which generally operate from 2.7V to 4.2V. The TPS65950 power management controller takes the MAIN\_BATTERY rail input and creates all onboard voltages. If MAIN\_BATTERY is taken away, the processor cannot be woken up and has to go through a power-on reset sequence once MAIN\_BATTERY returns.

#### 5.6.2 BACKUP\_BATT

The BACKUP\_BATT power rail is used to power the onboard TPS65950 PMIC, power management state machine, and RTC circuit when MAIN\_BATTERY is not present. Always power this rail to maintain the clock and power state of the product. A lithium-ion coin cell typically supplies power to this rail. The TPS65950 PMIC overrides this input when MAIN\_BATTERY is applied.

#### 5.7 System Power Management

Good power management design is important in any system development and embedded system design is no exception. In embedded system design, power management is typically one of the most complicated areas due to the dramatic effect it has on product cost, performance, usability, and overall customer satisfaction. Many factors affect a power-efficient hardware design: power supply selection (efficiency), clocking design, IC and component selection, etc. The DM3730/AM3703 Torpedo SOM was designed with these aspects in mind, while also providing maximum flexibility in software and system integration.

On the DM3730/AM3703 Torpedo SOM, there are many different software configurations that drastically affect power consumption: microcontroller core clock frequency; bus clock frequency; peripheral clocks; bus modes; power-management states; peripheral power states and modes; product user scenarios; interrupt handling; and display settings (resolution, backlight, refresh, bits per pixel, etc). These settings are typically initialized in the startup software routines and may be modified later in the operating system and application software. Information for these items can be found in the appropriate documents such as the *LogicLoader v2.5 User Guide* or the specific BSP manual.

#### 5.7.1 T2 REGEN

T2\_REGEN is an open-drain output from the TPS65950 PMIC. It can be used to control power for external power ICs or LDOs during both startup sequencing and low-power modes where external supplies may be turned off for additional power savings. Please see the *TPS65950 OMAP Power Management and System Companion Device TRM* for more information.

#### **5.7.2 PWRON**

The PWRON signal may be used to power on/off the SOM only after MAIN\_BATTERY has been supplied to the SOM. Software must also set up the signal before it becomes a valid power switch. MAIN\_BATTERY must be supplied to the SOM at all times when using the PWRON signal to power on/off the SOM. Please see the *TPS65950 OMAP Power Management and System Companion Device TRM* for more information.

#### 5.8 Processor Power Management

The DM3730/AM3703 processor's power management scheme was designed for the cellular handset market. This means the static and dynamic power consumption has very flexible controls, allowing designers to tweak the processor to minimize end-product power consumption. Logic PD software BSPs take advantage of Dynamic Voltage and Frequency Scaling (DVFS), Adaptive Voltage Scaling (AVS), and Dynamic Power Switching (DPS) to maximize power savings.

**IMPORTANT NOTE:** Sections 5.8.1 through 5.8.4 provide an overview of the features of the DM3730/AM3703 processor. Please refer to the specific BSP manual or the *WP 491 DM3730/AM3703 Torpedo SOM Thermal Management* for more information about how each BSP supports these features. For additional information about the features themselves, see TI's *AM/DM37x Multimedia Device TRM*.

#### 5.8.1 Dynamic Voltage and Frequency Scaling

DVFS is a method of changing the operating performance point (OPP) depending upon the task that is being performed. The lowest OPP is chosen such that a task will be completed in a given amount of time. By choosing the lowest OPP necessary to complete a task, a large amount of power is saved.

#### 5.8.2 Adaptive Voltage Scaling

AVS is implemented on the DM3730/AM3703 processor through SmartReflex. AVS fine tunes the core voltages (VDD1\_CORE and VDD2\_CORE) to match the current operating frequency. AVS accounts for silicon differences between processors and allows the core voltages to run at the minimum voltage level on a per-silicon basis.

#### 5.8.3 Dynamic Power Switching

DPS can be used to put sections of the DM3730/AM3703 processor into low-power states while it is waiting for a new task—for example, waiting for a timer or peripheral interrupt. DPS is different from DVFS and AVS because the power savings are realized while the DM3730/AM3703 processor is idle rather than actively completing a task.

#### 5.8.4 Static Power Consumption Management

Static power consumption is managed by putting the DM3730/AM3703 processor into standby, suspend, or deep sleep modes. This helps reduce static power loss due to leakage in the processor and reduce overall power by turning off sections of the processor (the wakeup domain is kept powered). Using standby and suspend provides a quicker wakeup response than does completely cutting power to the SOM.

#### 5.9 Boot Modes

The DM3730/AM3703 processor provides the option of booting from multiple sources. The boot mode is controlled by the SYS\_BOOT pins of the processor. SYS\_BOOT0, SYS\_BOOT1 and SYS\_BOOT3-SYS\_BOOT5 are available off-board through the SOM's J1 and J2 connectors. Please see TI's *AM/DM37x Multimedia Device TRM* for further information. Common boot options are shown in Table 5.1 below.

**NOTE:** The SYS\_BOOT pins of the processor are shared with the parallel display interface. Take care to ensure the boot strapping does not interfere with the display operation; also, the display must not interfere with the SYS\_BOOT pins during reset.

Table 5.1: Signals for Multiple Boot Sources

|           | DM3730/AM3703 Processor Pins | Boot Method                    |

|-----------|------------------------------|--------------------------------|

| Default   | SYS_BOOT[6:0] =1101111       | USB, UART3, MMC1, NAND         |

| Alternate | SYS_BOOT[6:0] =1001111       | NAND, USB, UART3, MMC1         |

| Alternate | SYS_BOOT[6:0] =1001110       | XIPwait, DOC, USB, UART3, MMC1 |

| Alternate | SYS_BOOT[6:0] =1000110       | MMC1, USB                      |

#### 5.10 ESD Considerations

The DM3730/AM3703 Torpedo SOM was designed to interface to a customer's baseboard, while remaining low cost and adaptable to many different applications. The DM3730/AM3703 Torpedo SOM does not provide any onboard ESD protection circuitry—this must be provided by the product it is used in. Logic PD has extensive experience in designing products with ESD requirements. Please contact Logic PD if you need any assistance in ESD design considerations.

## 6 Memory & I/O Mapping

On the DM3730/AM3703 processor, all address mapping for the GPMC chip select signals is listed below. Mapped chip select signals for the processor are available as outputs and are assigned as described in Table 6.1.

Table 6.1: Chip Select Signals

| Chip Select | Device/Feature | Notes                                             |

|-------------|----------------|---------------------------------------------------|

| nCS0        | PoP NAND       | Boot chip select for PoP NAND device.             |

| nCS1        | uP_nCS1        | Available for use by an off-board external device |

| nCS2        | uP_nCS2        | Available for use by an off-board external device |

| nCS3        | uP_nCS3        | Available for use by an off-board external device |

| nCS4        | uP_nCS4        | Available for use by an off-board external device |

| nCS5        | uP_nCS5        | Available for use by an off-board external device |

| nCS6        | uP_nCS6        | Available for use by an off-board external device |

**NOTE:** Memory addresses for chip selects on the DM3730/AM3703 Torpedo SOM are configurable by software; therefore, precise address locations cannot be provided.

## 7 Pin Descriptions & Functions

**IMPORTANT NOTE:** The following pin descriptions and states are provided for the default pin usage for the Torpedo form factor. Many of the signals defined in the connector tables can be configured as input or outputs—most GPIOs on the DM3730/AM3703 processor can be configured as either inputs or outputs—and have different functions. The *I/O* column of the pin description tables below refers to the default signal usage; processor I/O capability may be different. It is critical to review all signals in the final design (both electrical and software) to verify the necessary configuration (external pull-ups/pull-downs).

**IMPORTANT NOTE:** Please pay special attention to the reference voltage used to power each signal in the table below, especially when used as a GPIO. Not all power rails coming out of the TPS65950 PMIC are on by default and may need to be enabled through software. Reference voltages for DM3730/AM3703 processor signals can be found in Table 2-1 of TI's *DM3730*, *DM3725 Digital Media Processors Datasheet* or *AM3715*, *AM3703 Sitara ARM Microprocessor Datasheet*.

#### 7.1 J1 Connector 100-Pin Descriptions

| J1   |             |                    |                                      |     |                            |                                                                                                                                                                                         |

|------|-------------|--------------------|--------------------------------------|-----|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin# | Signal Name | BGA Ball#          | Processor Signal                     | 1/0 | Voltage                    | Description                                                                                                                                                                             |

| 1    | uP_nWE      | F4                 | GPMC_nWE                             | 0   | 1.8V                       | Low indicates processor is writing.<br>High indicates processor is<br>reading. (See notes 1 & 2)                                                                                        |

| 2    | CODEC_OUTL  | B4 (PMIC)          | HSOL (PMIC)                          | 0   | max 2.7V                   | Left channel headset out.                                                                                                                                                               |

| 3    | VMMC1       | K25<br>C2 (PMIC)   | VDDS_MMC1<br>VMMC1.OUT (PMIC)        |     | 3.0V<br>(configurable)     | MMC/SD1 interface voltage reference output.                                                                                                                                             |

| 4    | CODEC_INR   | G1 (PMIC)          | AUXR (PMIC)                          | I   | max 2.7V                   | Auxiliary right channel line in.                                                                                                                                                        |

| 5    | PWRON       | A11 (PMIC)         | PWRON (PMIC)                         |     | Max 4.5V<br>(MAIN_BATTERY) | Active low. Software can use this signal as an interrupt to transition to RUN state from lower power states. Software is required for proper operation. This signal has a 4.7K pull up. |

| 6    | CODEC_INL   | F1 (PMIC)          | AUXL (PMIC)                          | Ι   | max 2.7V                   | Auxiliary left channel line in.                                                                                                                                                         |

| 7    | uP_A9       | L3                 | GPMC_A9/<br>SYS_nDMAREQ2/<br>GPIO_42 | 0   | 1.8V                       | Processor GPMC bus address bit 9.                                                                                                                                                       |

| 8    | MIC_IN      | E3 (PMIC)          | HSMIC.P (PMIC)                       | I   | max 2.7V                   | Microphone input.                                                                                                                                                                       |

| 9    | uP_nCS0     | G4                 | GPMC_nCS0                            | 0   | 1.8V                       | uP_nCS0 is used by the PoP<br>NAND flash device. This signal<br>MUST be left unconnected, unless<br>the PoP chip does not contain<br>NAND. (See note 1)                                 |

| 10   | CODEC_OUTR  | B5 (PMIC)          | HSOR (PMIC)                          | 0   | max 2.7V                   | Right channel headset out.                                                                                                                                                              |

| 11   | uP_nCS1     | Н3                 | GPMC_nCS1/GPIO_52                    | 0   | 1.8V                       | External chip select available for customer use.                                                                                                                                        |

| 12   | DGND        | (See<br>Schematic) | (See Schematic)                      | ı   | GND                        | Ground. Connect to digital ground.                                                                                                                                                      |

| 13   | uP_A8       | M3                 | GPMC_A8/GPIO_41                      | 0   | 1.8V                       | Processor GPMC bus address bit 8.                                                                                                                                                       |

| J1   |              |                    |                           |     |           |                                                                                                                                                                                                                                                                                  |

|------|--------------|--------------------|---------------------------|-----|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin# | Signal Name  | BGA Ball#          | Processor Signal          | I/O | Voltage   | Description                                                                                                                                                                                                                                                                      |

| 14   | MAIN_BATTERY | (See<br>Schematic) | (See Schematic)           | I   | max 4.5V  | External power source input. This signal should be driven directly by a single cell lithium-ion battery or a fixed regulated power source.                                                                                                                                       |

| 15   | uP_nOE       | G2                 | GPMC_nOE                  | 0   | 1.8V      | Active low. Used to indicate processor is reading from external devices. (See notes 1 & 2)                                                                                                                                                                                       |

| 16   | MAIN_BATTERY | (See<br>Schematic) | (See Schematic)           |     | max 4.5V  | External power source input. This signal should be driven directly by a single cell lithium-ion battery or a fixed regulated power source.                                                                                                                                       |

|      | DGND         | (See<br>Schematic) | (See Schematic)           | ı   | GND       | Ground. Connect to digital ground.                                                                                                                                                                                                                                               |

| 18   | MAIN_BATTERY | (See<br>Schematic) | (See Schematic)           | ı   | max 4.5V  | External power source input. This signal should be driven directly by a single cell lithium-ion battery or a fixed regulated power source.                                                                                                                                       |

| 19   | uP_BUS_CLK   | T4                 | GPMC_CLK/GPIO_59          | 0   | 1.8V      | Processor bus clock. Frequency varies based on software setup. <b>NOTE</b> uP_BUS_CLK is only active on bus transactions, it does not run continuously. See Tl's <i>AM/DM37x TRM</i> and datasheets for additional information.                                                  |

| 20   | MAIN_BATTERY | (See<br>Schematic) | (See Schematic)           | ı   | max 4.5V  | External power source input. This signal should be driven directly by a single cell lithium-ion battery or a fixed regulated power source.                                                                                                                                       |

| 21   | uP_nBE1      | U3                 | GPMC_nBE1/GPIO_61         | 0   | 1.8V      | Processor bus Byte Lane Enable 1 bits [15:8].                                                                                                                                                                                                                                    |

| 22   | DGND         | (See<br>Schematic) | (See Schematic)           | ı   | GND       | Ground. Connect to digital ground.                                                                                                                                                                                                                                               |

| 23   | uP_nADV_ALE  | F3                 | GPMC_nADV_ALE             | 0   | 1.8V      | Processor GPMC address valid or address latch enable signal. (See notes 1 & 2)                                                                                                                                                                                                   |

| 24   | BACKUP_BATT  | M14 (PMIC)         | BKBAT (PMIC)              | ı   | 1.8V-3.3V | External input that supplies power to the onboard power management controller and RTC interface. This signal should be powered by a coin-cell type battery or an alwayson power source.                                                                                          |

| 25   | uP_nBE0      | G3                 | GPMC_nBE0_CLE/<br>GPIO_60 | 0   | 1.8V      | Processor bus Byte Lane Enable 0 bits [7:0]. (See notes 1 & 2)                                                                                                                                                                                                                   |

| 26   | uP_nWAIT     | M8                 | GPMC_WAIT0                | I   | 1.8V      | Active low. Processor bus GPMC_WAIT0 signal. Used to extend bus transactions beyond programmed wait states. The external device signals completion of the cycle by deasserting the uP_nWAIT signal. This signal is connected to the PoP NAND flash R/B signal. (See notes 1 & 2) |

| 27   | DGND         | (See<br>Schematic) | (See Schematic)           | I   | GND       | Ground. Connect to digital ground.                                                                                                                                                                                                                                               |

| J1<br>Pin# | Signal Name | BGA Ball#  | Processor Signal                                                        | I/O | Voltage | Description                                                                                                                                                                                                                       |

|------------|-------------|------------|-------------------------------------------------------------------------|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28         | uP_nCS6     | P8         | GPMC_nCS6/<br>SYS_nDMAREQ3/<br>McBSP4_DX/<br>GPT11_PWM_EVT/<br>GPIO_57  | 0   |         | External chip select available for customer use.                                                                                                                                                                                  |

|            | uP_D8       | H2         | GPMC_D8/GPIO_44                                                         |     | 1.8V    | Processor GPMC bus data bit 8.<br>(See notes 1 & 2)                                                                                                                                                                               |

| 30         | uP_DREQ0    | J8<br>AG11 | GPMC_WAIT3/<br>SYS_nDMAREQ1/<br>UART4_RX/GPIO_65<br>POP_INT0_FT         | I   |         | DMA Request signal for DMA4. Connected to SYS_nDMAREQ1 of the DM3730. <b>NOTE</b> : This signal is shared with the PoP NAND chip's LOCK pin. This signal should be left floating at power-on to avoid conflict. (See notes 1 & 2) |

| 31         | uP_D9       | K2         | GPMC_D9/GPIO_45                                                         | I/O | 1.8V    | Processor GPMC bus data bit 9.<br>(See notes 1 & 2)                                                                                                                                                                               |

| 32         | uP_nCS5     | R8         | GPMC_nCS5/<br>SYS_nDMAREQ2/<br>McBSP4_DR/<br>GPT10_PWM_EVT/<br>GPIO_56  | 0   | 1.8V    | External chip select available for customer use.                                                                                                                                                                                  |

| 33         | uP_D2       | L2         | GPMC_D2                                                                 | I/O | 1.8V    | Processor GPMC bus data bit 2.<br>(See notes 1 & 2)                                                                                                                                                                               |

|            | uP_nCS4     | Т8         | GPMC_nCS4/<br>SYS_nDMAREQ1/<br>McBSP4_CLKX/<br>GPT9_PWM_EVT/<br>GPIO_55 | 0   |         | External chip select available for customer use.                                                                                                                                                                                  |

| 35         | uP_D0       | K1         | GPMC_D0                                                                 | I/O | 1.8V    | Processor GPMC bus data bit 0.<br>(See notes 1 & 2)                                                                                                                                                                               |

|            | uP_nCS3     | U8         | GPMC_nCS3/<br>SYS_nDMAREQ0/<br>GPIO_54                                  |     |         | External chip select available for customer use.                                                                                                                                                                                  |

| 37         | uP_D1       | L1         | GPMC_D1                                                                 | I/O | 1.8V    | Processor GPMC bus data bit 1.<br>(See notes 1 & 2)                                                                                                                                                                               |

| 38         | uP_A10      | К3         | GPMC_A10/<br>SYS_nDMAREQ3/<br>GPIO_43                                   | 0   | 1.8V    | Processor GPMC bus address bit 10.                                                                                                                                                                                                |

| 39         | uP_D3       | P2         | GPMC_D3                                                                 | I/O | 1.8V    | Processor GPMC bus data bit 3. (See notes 1 & 2)                                                                                                                                                                                  |

| 40         | uP_nCS2     | V8         | GPMC_nCS2/GPIO_53                                                       | 0   | 1.8V    | External chip select available for customer use.                                                                                                                                                                                  |

| 41         | uP_D12      | R2         | GPMC_D12/GPIO_48                                                        | I/O | 1.8V    | Processor GPMC bus data bit 12. (See notes 1 & 2)                                                                                                                                                                                 |

| 42         | uP_A4       | K4         | GPMC_A4/GPIO_37                                                         | 0   | 1.8V    | Processor GPMC bus address bit 4.                                                                                                                                                                                                 |

| 43         | uP_D10      | P1         | GPMC_D10/GPIO_46                                                        | I/O | 1.8V    | Processor GPMC bus data bit 10. (See notes 1 & 2)                                                                                                                                                                                 |

| 44         | uP_A3       | L4         | GPMC_A3/GPIO_36                                                         | 0   | 1.8V    | Processor GPMC bus address bit 3.                                                                                                                                                                                                 |

| 45         | uP_D11      | R1         | GPMC_D11/GPIO_47                                                        | I/O | 1.8V    | Processor GPMC bus data bit 11. (See notes 1 & 2)                                                                                                                                                                                 |

| J1<br>Pin# | Signal Name | BGA Ball#          | Processor Signal                                                                              | I/O | Voltage | Description                                         |

|------------|-------------|--------------------|-----------------------------------------------------------------------------------------------|-----|---------|-----------------------------------------------------|

| 46         | uP_A2       | M4                 | GPMC_A2/GPIO_35                                                                               | 0   | 1.8V    | Processor GPMC bus address bit 2.                   |

| 47         | uP_D13      | T2                 | GPMC_D13/GPIO_49                                                                              | I/O | 1.8V    | Processor GPMC bus data bit 13. (See notes 1 & 2)   |

| 48         | uP_A1       | N4                 | GPMC_A1/GPIO_34                                                                               | 0   | 1.8V    | Processor GPMC bus address bit 1.                   |

| 49         | uP_D4       | T1                 | GPMC_D4                                                                                       | I/O | 1.8V    | Processor GPMC bus data bit 4. (See notes 1 & 2)    |

| 50         | uP_A7       | N3                 | GPMC_A7/GPIO_40                                                                               | 0   | 1.8V    | Processor GPMC bus address bit 7.                   |

| 51         | MCSPI2_CS1  | V3                 | McSPI2_CS1/<br>GPT8_PWM_EVT/<br>HSUSB2_TLL_DATA3/<br>USUSB2_DATA3/<br>MM2_TXEN_N/<br>GPIO_182 | 0   | 1.8V    | McSPI2 interface chip select 1 output.              |

| 52         | uP_A6       | R3                 | GPMC_A6/GPIO_39                                                                               | 0   | 1.8V    | Processor GPMC bus address bit 6.                   |

| 53         | uP_D6       | V2                 | GPMC_D6                                                                                       | I/O | 1.8V    | Processor GPMC bus data bit 6. (See notes 1 & 2)    |

| 54         | uP_A5       | T3                 | GPMC_A5/GPIO_38                                                                               | 0   | 1.8V    | Processor GPMC bus address bit 5.                   |

| 55         | uP_D7       | W2                 | GPMC_D7                                                                                       | I/O | 1.8V    | Processor GPMC bus data bit 7.<br>(See notes 1 & 2) |

| 56         | MCSPI2_SOMI | <b>Y</b> 3         | McSPI2_SOMI/<br>GPT10_PWM_EVT/<br>HSUSB2_TLL_DATA5/<br>HSUSB2_DATA5/<br>GPIO_180              | _   | 1.8V    | McSPI2 interface receive input.                     |

| 57         | uP_D5       | V1                 | GPMC_D5                                                                                       | I/O | 1.8V    | Processor GPMC bus data bit 5.<br>(See notes 1 & 2) |

| 58         | MCSPI2_CS0  | Y4                 | McSPI2_CS0/<br>GPT11_PWM_EVT/<br>HSUSB2_TLL_DATA6/<br>HSUSB2_DATA6/<br>GPIO_181               | 0   | 1.8V    | McSPI2 interface chip select 0 output.              |

| 59         | uP_D14      | W1                 | GPMC_D14/GPIO_50                                                                              | I/O | 1.8V    | Processor GPMC bus data bit 14. (See notes 1 & 2)   |

| 60         | MCSPI1_SOMI | AA4                | McSPI1_SOMI/<br>MMC2_DAT6/GPIO_173                                                            | ı   | 1.8V    | McSPI1 interface receive input.                     |

| 61         | DGND        | (See<br>Schematic) | (See Schematic)                                                                               | ı   | GND     | Ground. Connect to digital ground.                  |

| 62         | MCBSP4_DR   | AD1                | McBSP4_DR/<br>SSI1_FLAG_RX/<br>HSUSB3_TLL_DATA0/<br>MM3_RXRCV/<br>GPIO_153                    | 1   | 1.8V    | McBSP4 interface receive input.                     |

| 63         | uP_D15      | Y1                 | GPMC_D15/GPIO_51                                                                              | I/O | 1.8V    | Processor GPMC bus data bit 15. (See notes 1 & 2)   |

| 64         | MCSPI1_CLK  | AB3                | McSPI1_CLK/<br>MMC2_DAT4GPIO_171                                                              | 0   | 1.8V    | McSPI1 serial clock signal.                         |

| J1<br>Pin# | Signal Name                                   | BGA Ball#         | Processor Signal                                                          | I/O | Voltage  | Description                                                                                                          |

|------------|-----------------------------------------------|-------------------|---------------------------------------------------------------------------|-----|----------|----------------------------------------------------------------------------------------------------------------------|

|            |                                               |                   | McSPI2_SIMO/<br>GPT9_PWM_EVT/<br>HSUSB2_TLL_DATA4/<br>HSUSB2_DATA4/       |     |          | ·                                                                                                                    |

|            | MCSPI2_SIMO                                   | Y2                | GPIO_179<br>McSPI1_SIMO/                                                  |     |          | McSPI2 interface transmit output.                                                                                    |