# LPC1769/68/67/66/65/64/63

32-bit ARM Cortex-M3 microcontroller; up to 512 kB flash and 64 kB SRAM with Ethernet, USB 2.0 Host/Device/OTG, CAN

Rev. 9 — 10 August 2012

**Product data sheet**

# 1. General description

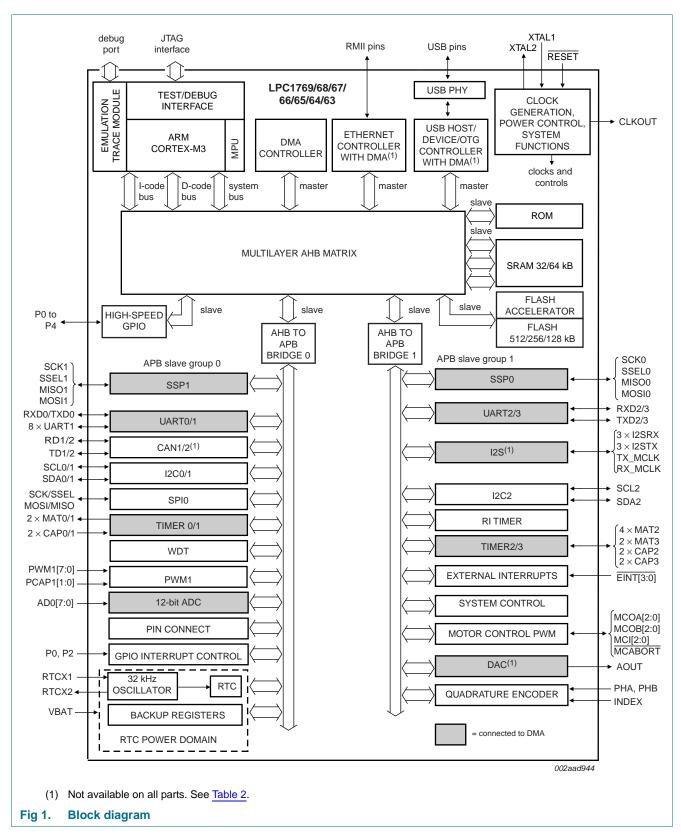

The LPC1769/68/67/66/65/64/63 are ARM Cortex-M3 based microcontrollers for embedded applications featuring a high level of integration and low power consumption. The ARM Cortex-M3 is a next generation core that offers system enhancements such as enhanced debug features and a higher level of support block integration.

The LPC1768/67/66/65/64/63 operate at CPU frequencies of up to 100 MHz. The LPC1769 operates at CPU frequencies of up to 120 MHz. The ARM Cortex-M3 CPU incorporates a 3-stage pipeline and uses a Harvard architecture with separate local instruction and data buses as well as a third bus for peripherals. The ARM Cortex-M3 CPU also includes an internal prefetch unit that supports speculative branching.

The peripheral complement of the LPC1769/68/67/66/65/64/63 includes up to 512 kB of flash memory, up to 64 kB of data memory, Ethernet MAC, USB Device/Host/OTG interface, 8-channel general purpose DMA controller, 4 UARTs, 2 CAN channels, 2 SSP controllers, SPI interface, 3 I<sup>2</sup>C-bus interfaces, 2-input plus 2-output I<sup>2</sup>S-bus interface, 8-channel 12-bit ADC, 10-bit DAC, motor control PWM, Quadrature Encoder interface, four general purpose timers, 6-output general purpose PWM, ultra-low power Real-Time Clock (RTC) with separate battery supply, and up to 70 general purpose I/O pins.

The LPC1769/68/67/66/65/64/63 are pin-compatible to the 100-pin LPC236x ARM7-based microcontroller series.

# 2. Features and benefits

- ARM Cortex-M3 processor, running at frequencies of up to 100 MHz (LPC1768/67/66/65/64/63) or of up to 120 MHz (LPC1769). A Memory Protection Unit (MPU) supporting eight regions is included.

- ARM Cortex-M3 built-in Nested Vectored Interrupt Controller (NVIC).

- Up to 512 kB on-chip flash programming memory. Enhanced flash memory accelerator enables high-speed 120 MHz operation with zero wait states.

- In-System Programming (ISP) and In-Application Programming (IAP) via on-chip bootloader software.

- On-chip SRAM includes:

- 32/16 kB of SRAM on the CPU with local code/data bus for high-performance CPU access.

- Two/one 16 kB SRAM blocks with separate access paths for higher throughput. These SRAM blocks may be used for Ethernet, USB, and DMA memory, as well as for general purpose CPU instruction and data storage.

- Eight channel General Purpose DMA controller (GPDMA) on the AHB multilayer matrix that can be used with SSP, I<sup>2</sup>S-bus, UART, Analog-to-Digital and Digital-to-Analog converter peripherals, timer match signals, and for memory-to-memory transfers.

- Multilayer AHB matrix interconnect provides a separate bus for each AHB master. AHB masters include the CPU, General Purpose DMA controller, Ethernet MAC, and the USB interface. This interconnect provides communication with no arbitration delays.

- Split APB bus allows high throughput with few stalls between the CPU and DMA.

- Serial interfaces:

- Ethernet MAC with RMII interface and dedicated DMA controller. (Not available on all parts, see <u>Table 2</u>.)

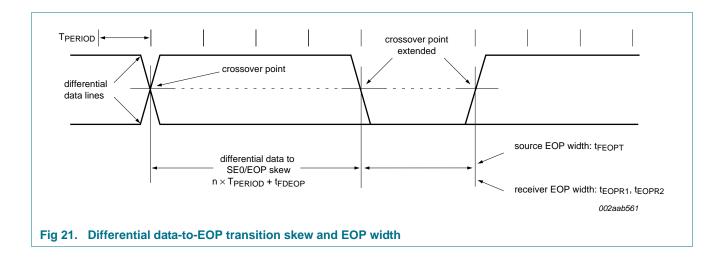

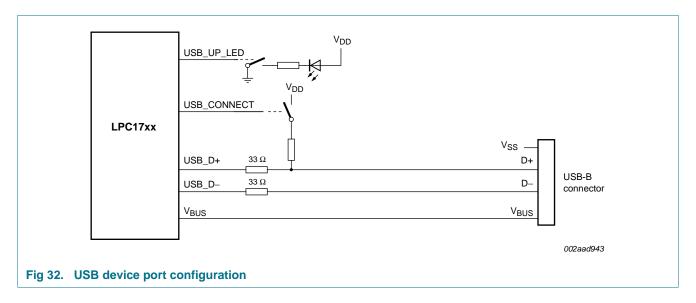

- ◆ USB 2.0 full-speed device/Host/OTG controller with dedicated DMA controller and on-chip PHY for device, Host, and OTG functions. (Not available on all parts, see <a href="Table 2">Table 2</a>.)

- Four UARTs with fractional baud rate generation, internal FIFO, and DMA support.

One UART has modem control I/O and RS-485/EIA-485 support, and one UART has IrDA support.

- ◆ CAN 2.0B controller with two channels. (Not available on all parts, see Table 2.)

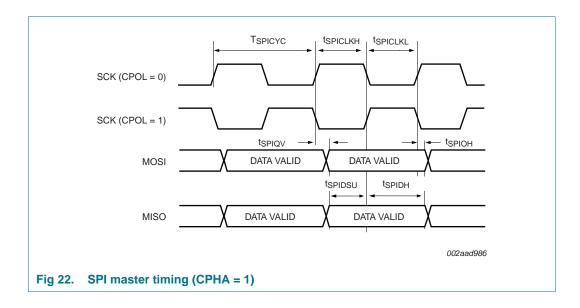

- SPI controller with synchronous, serial, full duplex communication and programmable data length.

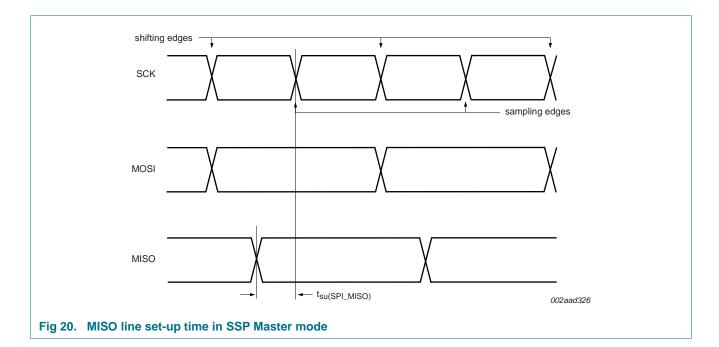

- ◆ Two SSP controllers with FIFO and multi-protocol capabilities. The SSP interfaces can be used with the GPDMA controller.

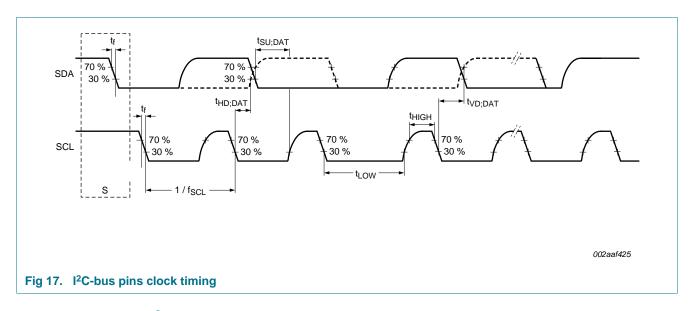

- ◆ Three enhanced I²C bus interfaces, one with an open-drain output supporting full I²C specification and Fast mode plus with data rates of 1 Mbit/s, two with standard port pins. Enhancements include multiple address recognition and monitor mode.

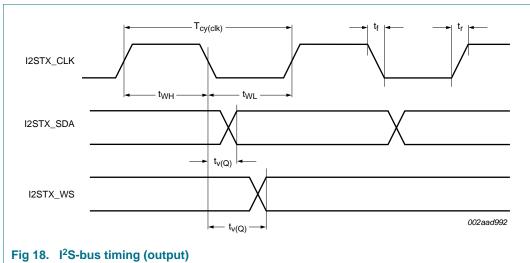

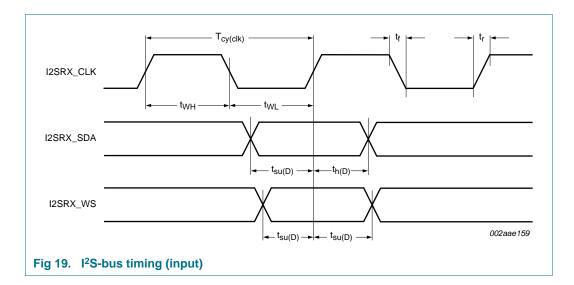

- ◆ I<sup>2</sup>S (Inter-IC Sound) interface for digital audio input or output, with fractional rate control. The I<sup>2</sup>S-bus interface can be used with the GPDMA. The I<sup>2</sup>S-bus interface supports 3-wire and 4-wire data transmit and receive as well as master clock input/output. (Not available on all parts, see Table 2.)

- Other peripherals:

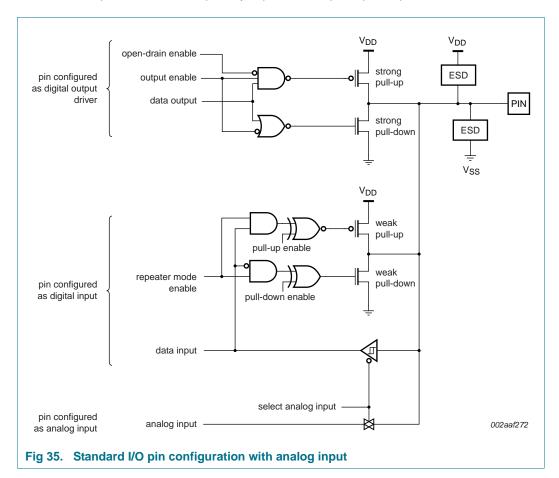

- ◆ 70 (100 pin package) General Purpose I/O (GPIO) pins with configurable pull-up/down resistors. All GPIOs support a new, configurable open-drain operating mode. The GPIO block is accessed through the AHB multilayer bus for fast access and located in memory such that it supports Cortex-M3 bit banding and use by the General Purpose DMA Controller.

- ◆ 12-bit Analog-to-Digital Converter (ADC) with input multiplexing among eight pins, conversion rates up to 200 kHz, and multiple result registers. The 12-bit ADC can be used with the GPDMA controller.

- 10-bit Digital-to-Analog Converter (DAC) with dedicated conversion timer and DMA support. (Not available on all parts, see Table 2)

- Four general purpose timers/counters, with a total of eight capture inputs and ten compare outputs. Each timer block has an external count input. Specific timer events can be selected to generate DMA requests.

- One motor control PWM with support for three-phase motor control.

- Quadrature encoder interface that can monitor one external quadrature encoder.

- One standard PWM/timer block with external count input.

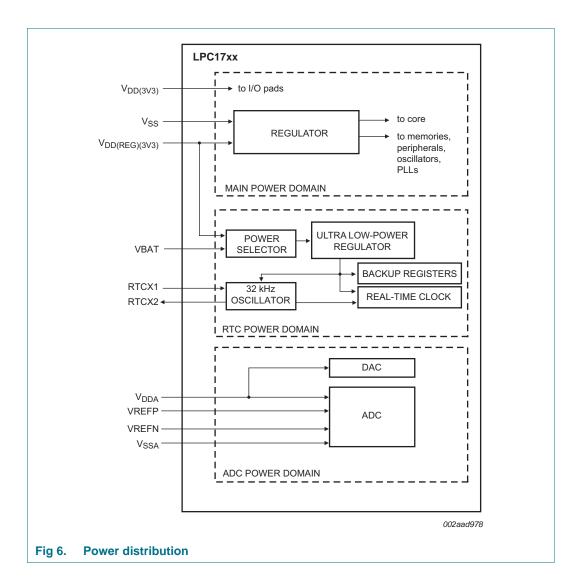

- RTC with a separate power domain and dedicated RTC oscillator. The RTC block includes 20 bytes of battery-powered backup registers.

- WatchDog Timer (WDT). The WDT can be clocked from the internal RC oscillator, the RTC oscillator, or the APB clock.

- ◆ ARM Cortex-M3 system tick timer, including an external clock input option.

- Repetitive interrupt timer provides programmable and repeating timed interrupts.

- Each peripheral has its own clock divider for further power savings.

- Standard JTAG test/debug interface for compatibility with existing tools. Serial Wire Debug and Serial Wire Trace Port options.

- Emulation trace module enables non-intrusive, high-speed real-time tracing of instruction execution.

- Integrated PMU (Power Management Unit) automatically adjusts internal regulators to minimize power consumption during Sleep, Deep sleep, Power-down, and Deep power-down modes.

- Four reduced power modes: Sleep, Deep-sleep, Power-down, and Deep power-down.

- Single 3.3 V power supply (2.4 V to 3.6 V).

- Four external interrupt inputs configurable as edge/level sensitive. All pins on Port 0 and Port 2 can be used as edge sensitive interrupt sources.

- Non-maskable Interrupt (NMI) input.

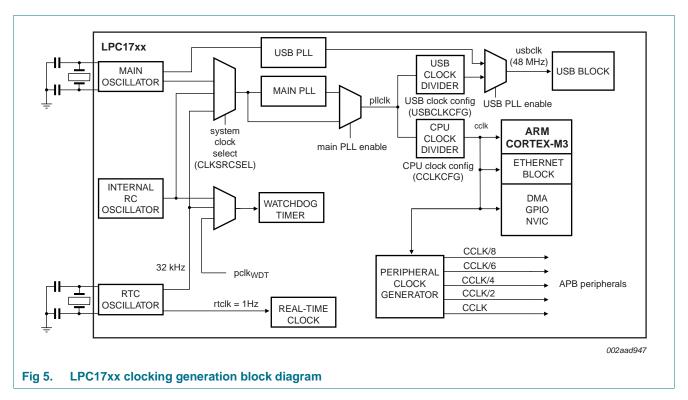

- Clock output function that can reflect the main oscillator clock, IRC clock, RTC clock, CPU clock, and the USB clock.

- The Wake-up Interrupt Controller (WIC) allows the CPU to automatically wake up from any priority interrupt that can occur while the clocks are stopped in deep sleep, Power-down, and Deep power-down modes.

- Processor wake-up from Power-down mode via any interrupt able to operate during Power-down mode (includes external interrupts, RTC interrupt, USB activity, Ethernet wake-up interrupt, CAN bus activity, Port 0/2 pin interrupt, and NMI).

- Brownout detect with separate threshold for interrupt and forced reset.

- Power-On Reset (POR).

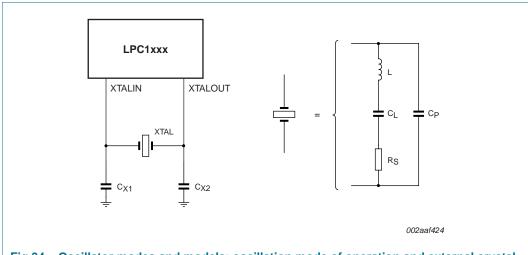

- Crystal oscillator with an operating range of 1 MHz to 25 MHz.

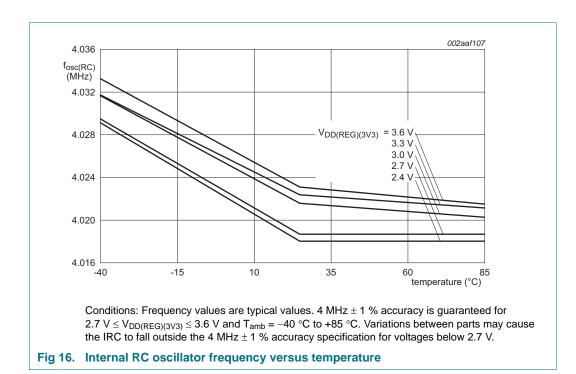

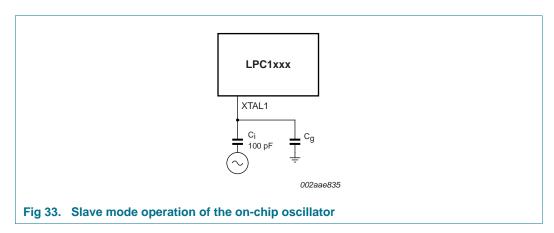

- 4 MHz internal RC oscillator trimmed to 1 % accuracy that can optionally be used as a system clock.

- PLL allows CPU operation up to the maximum CPU rate without the need for a high-frequency crystal. May be run from the main oscillator, the internal RC oscillator, or the RTC oscillator.

- USB PLL for added flexibility.

- Code Read Protection (CRP) with different security levels.

- Unique device serial number for identification purposes.

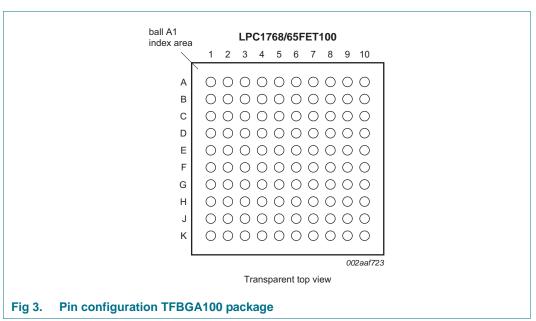

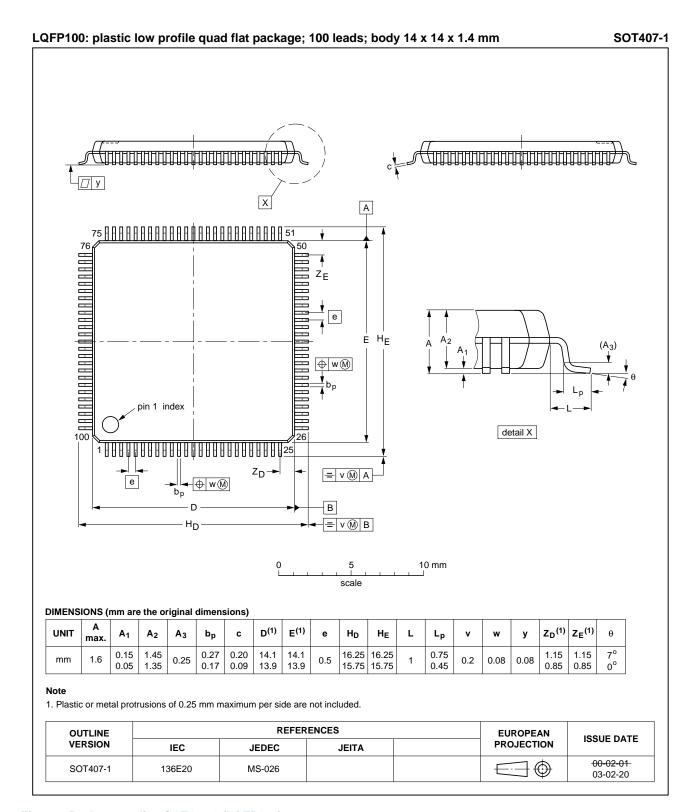

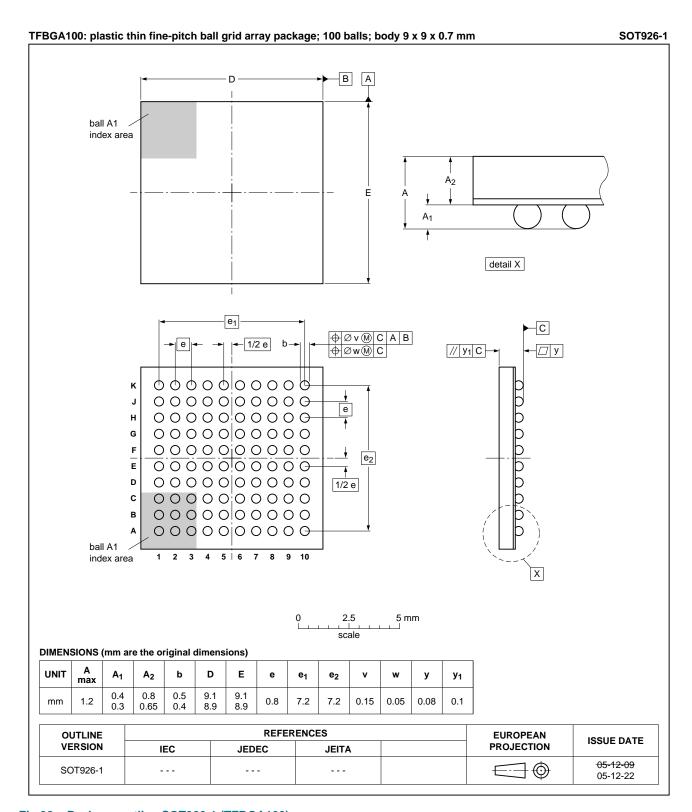

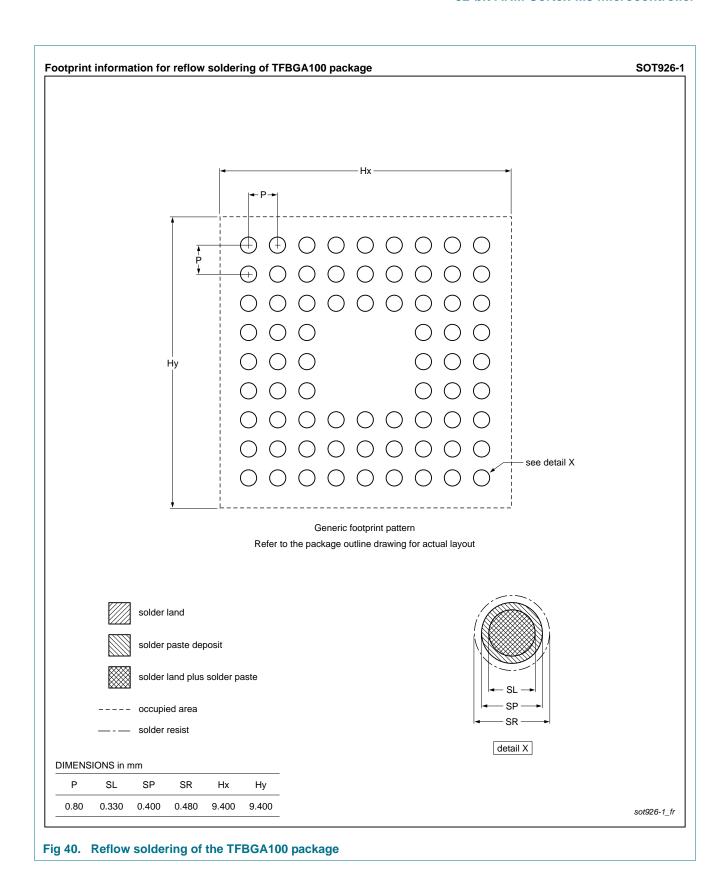

- Available as LQFP100 (14 mm  $\times$  14 mm  $\times$  1.4 mm) and TFBGA100<sup>1</sup> (9 mm  $\times$  9 mm  $\times$  0.7 mm) package.

<sup>1.</sup> LPC1768/65 only.

# 3. Applications

- eMetering

- Lighting

- Industrial networking

- Alarm systems

- White goods

- Motor control

# 4. Ordering information

Table 1. Ordering information

| Type number   | Package  |                                                                                         |          |  |  |  |  |  |  |  |  |

|---------------|----------|-----------------------------------------------------------------------------------------|----------|--|--|--|--|--|--|--|--|

|               | Name     | Description                                                                             | Version  |  |  |  |  |  |  |  |  |

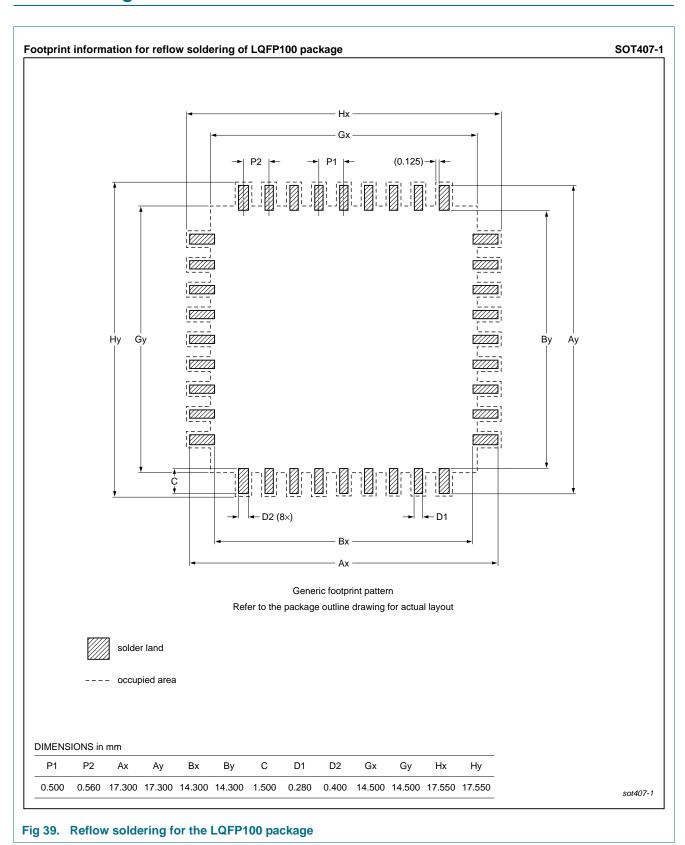

| LPC1769FBD100 | LQFP100  | plastic low profile quad flat package; 100 leads; body $14 \times 14 \times 1.4$ mm     | SOT407-1 |  |  |  |  |  |  |  |  |

| LPC1768FBD100 | LQFP100  | plastic low profile quad flat package; 100 leads; body 14 $\times$ 14 $\times$ 1.4 mm   | SOT407-1 |  |  |  |  |  |  |  |  |

| LPC1768FET100 | TFBGA100 | plastic thin fine-pitch ball grid array package; 100 balls; body $9\times9\times0.7$ mm | SOT926-1 |  |  |  |  |  |  |  |  |

| LPC1767FBD100 | LQFP100  | plastic low profile quad flat package; 100 leads; body 14 $\times$ 14 $\times$ 1.4 mm   | SOT407-1 |  |  |  |  |  |  |  |  |

| LPC1766FBD100 | LQFP100  | plastic low profile quad flat package; 100 leads; body 14 $\times$ 14 $\times$ 1.4 mm   | SOT407-1 |  |  |  |  |  |  |  |  |

| LPC1765FBD100 | LQFP100  | plastic low profile quad flat package; 100 leads; body 14 $\times$ 14 $\times$ 1.4 mm   | SOT407-1 |  |  |  |  |  |  |  |  |

| LPC1765FET100 | TFBGA100 | plastic thin fine-pitch ball grid array package; 100 balls; body $9\times9\times0.7$ mm | SOT926-1 |  |  |  |  |  |  |  |  |

| LPC1764FBD100 | LQFP100  | plastic low profile quad flat package; 100 leads; body 14 $\times$ 14 $\times$ 1.4 mm   | SOT407-1 |  |  |  |  |  |  |  |  |

| LPC1763FBD100 | LQFP100  | plastic low profile quad flat package; 100 leads; body 14 $\times$ 14 $\times$ 1.4 mm   | SOT407-1 |  |  |  |  |  |  |  |  |

# 4.1 Ordering options

Table 2. Ordering options

| Type number   | Flash  | SRAM | √l in kB     |              | Ethernet USB |     | USB             | CAN | I <sup>2</sup> S | DAC | Maximum                       |

|---------------|--------|------|--------------|--------------|--------------|-----|-----------------|-----|------------------|-----|-------------------------------|

|               |        | CPU  | AHB<br>SRAM0 | AHB<br>SRAM1 | Total        |     |                 |     |                  |     | CPU<br>operating<br>frequency |

| LPC1769FBD100 | 512 kB | 32   | 16           | 16           | 64           | yes | Device/Host/OTG | 2   | yes              | yes | 120 MHz                       |

| LPC1768FBD100 | 512 kB | 32   | 16           | 16           | 64           | yes | Device/Host/OTG | 2   | yes              | yes | 100 MHz                       |

| LPC1768FET100 | 512 kB | 32   | 16           | 16           | 64           | yes | Device/Host/OTG | 2   | yes              | yes | 100 MHz                       |

| LPC1767FBD100 | 512 kB | 32   | 16           | 16           | 64           | yes | no              | no  | yes              | yes | 100 MHz                       |

| LPC1766FBD100 | 256 kB | 32   | 16           | 16           | 64           | yes | Device/Host/OTG | 2   | yes              | yes | 100 MHz                       |

| LPC1765FBD100 | 256 kB | 32   | 16           | 16           | 64           | no  | Device/Host/OTG | 2   | yes              | yes | 100 MHz                       |

| LPC1765FET100 | 256 kB | 32   | 16           | 16           | 64           | no  | Device/Host/OTG | 2   | yes              | yes | 100 MHz                       |

| LPC1764FBD100 | 128 kB | 16   | 16           | -            | 32           | yes | Device only     | 2   | no               | no  | 100 MHz                       |

| LPC1763FBD100 | 256 kB | 32   | 16           | 16           | 64           | no  | no              | no  | yes              | yes | 100 MHz                       |

# 5. Block diagram

# 6. Pinning information

# 6.1 Pinning

Table 3. Pin allocation table

| Pin | Symbol                           | Pin | Symbol                            | Pin | Symbol                    | Pin | Symbol                          |

|-----|----------------------------------|-----|-----------------------------------|-----|---------------------------|-----|---------------------------------|

| Rov | w A                              | •   |                                   |     |                           |     |                                 |

| 1   | TDO/SWO                          | 2   | P0[3]/RXD0/AD0[6]                 | 3   | V <sub>DD(3V3)</sub>      | 4   | P1[4]/ENET_TX_EN                |

| 5   | P1[10]/ENET_RXD1                 | 6   | P1[16]/ENET_MDC                   | 7   | V <sub>DD(REG)(3V3)</sub> | 8   | P0[4]/I2SRX_CLK/<br>RD2/CAP2[0] |

| 9   | P0[7]/I2STX_CLK/<br>SCK1/MAT2[1] | 10  | P0[9]/I2STX_SDA/<br>MOSI1/MAT2[3] | 11  | -                         | 12  | -                               |

| Rov | w B                              |     |                                   |     |                           |     |                                 |

| 1   | TMS/SWDIO                        | 2   | RTCK                              | 3   | V <sub>SS</sub>           | 4   | P1[1]/ENET_TXD1                 |

LPC1769\_68\_67\_66\_65\_64\_63

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2012. All rights reserved.

Table 3.

Pin allocation table ...continued

|     | Symbol                              |    | Symbol                              | Pin | Symbol                              | Pin | Symbol                                |

|-----|-------------------------------------|----|-------------------------------------|-----|-------------------------------------|-----|---------------------------------------|

| 5   | P1[9]/ENET_RXD0                     | 6  | P1[17]/<br>ENET_MDIO                | 7   | V <sub>SS</sub>                     | 8   | P0[6]/I2SRX_SDA/<br>SSEL1/MAT2[0]     |

| 9   | P2[0]/PWM1[1]/TXD1                  | 10 | P2[1]/PWM1[2]/RXD1                  | 11  | -                                   | 12  | -                                     |

| Rov | v C                                 |    |                                     |     |                                     |     |                                       |

| 1   | TCK/SWDCLK                          | 2  | TRST                                | 3   | TDI                                 | 4   | P0[2]/TXD0/AD0[7]                     |

| 5   | P1[8]/ENET_CRS                      | 6  | P1[15]/<br>ENET_REF_CLK             | 7   | P4[28]/RX_MCLK/<br>MAT2[0]/TXD3     | 8   | P0[8]/I2STX_WS/<br>MISO1/MAT2[2]      |

| 9   | V <sub>SS</sub>                     | 10 | V <sub>DD(3V3)</sub>                | 11  | -                                   | 12  | -                                     |

| Rov | v D                                 |    |                                     |     |                                     |     |                                       |

| 1   | P0[24]/AD0[1]/<br>I2SRX_WS/CAP3[1]  | 2  | P0[25]/AD0[2]/<br>I2SRX_SDA/TXD3    | 3   | P0[26]/AD0[3]/<br>AOUT/RXD3         | 4   | n.c.                                  |

| 5   | P1[0]/ENET_TXD0                     | 6  | P1[14]/ENET_RX_ER                   | 7   | P0[5]/I2SRX_WS/<br>TD2/CAP2[1]      | 8   | P2[2]/PWM1[3]/<br>CTS1/TRACEDATA[3]   |

| 9   | P2[4]/PWM1[5]/<br>DSR1/TRACEDATA[1] | 10 | P2[5]/PWM1[6]/<br>DTR1/TRACEDATA[0] | 11  | -                                   | 12  | -                                     |

| Rov | v E                                 |    |                                     |     |                                     |     |                                       |

| 1   | $V_{SSA}$                           | 2  | $V_{DDA}$                           | 3   | VREFP                               | 4   | n.c.                                  |

| 5   | P0[23]/AD0[0]/<br>I2SRX_CLK/CAP3[0] | 6  | P4[29]/TX_MCLK/<br>MAT2[1]/RXD3     | 7   | P2[3]/PWM1[4]/<br>DCD1/TRACEDATA[2] | 8   | P2[6]/PCAP1[0]/<br>RI1/TRACECLK       |

| 9   | P2[7]/RD2/RTS1                      | 10 | P2[8]/TD2/TXD2                      | 11  | -                                   | 12  | -                                     |

| Rov | v F                                 |    |                                     |     |                                     |     |                                       |

| 1   | VREFN                               | 2  | RTCX1                               | 3   | RESET                               | 4   | P1[31]/SCK1/<br>AD0[5]                |

| 5   | P1[21]/MCABORT/<br>PWM1[3]/SSEL0    | 6  | P0[18]/DCD1/<br>MOSI0/MOSI          | 7   | P2[9]/USB_CONNECT/<br>RXD2          | 8   | P0[16]/RXD1/<br>SSEL0/SSEL            |

| 9   | P0[17]/CTS1/<br>MISO0/MISO          | 10 | P0[15]/TXD1/<br>SCK0/SCK            | 11  | -                                   | 12  | -                                     |

| Rov | v G                                 |    |                                     |     |                                     |     |                                       |

| 1   | RTCX2                               | 2  | VBAT                                | 3   | XTAL2                               | 4   | P0[30]/USB_D-                         |

| 5   | P1[25]/MCOA1/<br>MAT1[1]            | 6  | P1[29]/MCOB2/<br>PCAP1[1]/MAT0[1]   | 7   | V <sub>SS</sub>                     | 8   | P0[21]/RI1/RD1                        |

| 9   | P0[20]/DTR1/SCL1                    | 10 | P0[19]/DSR1/SDA1                    | 11  | -                                   | 12  | -                                     |

| Rov | v H                                 |    |                                     |     |                                     |     |                                       |

| 1   | P1[30]/V <sub>BUS</sub> /<br>AD0[4] | 2  | XTAL1                               | 3   | P3[25]/MAT0[0]/<br>PWM1[2]          | 4   | P1[18]/USB_UP_LED/<br>PWM1[1]/CAP1[0] |

| 5   | P1[24]/MCl2/<br>PWM1[5]/MOSI0       | 6  | V <sub>DD(REG)(3V3)</sub>           | 7   | P0[10]/TXD2/<br>SDA2/MAT3[0]        | 8   | P2[11]/EINT1/<br>I2STX_CLK            |

| 9   | V <sub>DD(3V3)</sub>                | 10 | P0[22]/RTS1/TD1                     | 11  | -                                   | 12  | -                                     |

Table 3.

Pin allocation table ...continued

| Pin | Symbol                                | Pin | Symbol                           | Pin | Symbol                                  | Pin | Symbol                                |

|-----|---------------------------------------|-----|----------------------------------|-----|-----------------------------------------|-----|---------------------------------------|

| Rov | v J                                   |     |                                  |     |                                         |     |                                       |

| 1   | P0[28]/SCL0/<br>USB_SCL               | 2   | P0[27]/SDA0/<br>USB_SDA          | 3   | P0[29]/USB_D+                           | 4   | P1[19]/MCOA0/<br>USB_PPWR/<br>CAP1[1] |

| 5   | P1[22]/MCOB0/<br>USB_PWRD/<br>MAT1[0] | 6   | $V_{SS}$                         | 7   | P1[28]/MCOA2/<br>PCAP1[0]/<br>MAT0[0]   | 8   | P0[1]/TD1/RXD3/SCL1                   |

| 9   | P2[13]/ <u>EINT3</u> /<br>I2STX_SDA   | 10  | P2[10]/EINT0/NMI                 | 11  | -                                       | 12  | -                                     |

| Rov | v K                                   |     |                                  |     |                                         |     |                                       |

| 1   | P3[26]/STCLK/<br>MAT0[1]/PWM1[3]      | 2   | V <sub>DD(3V3)</sub>             | 3   | V <sub>SS</sub>                         | 4   | P1[20]/MCI0/<br>PWM1[2]/SCK0          |

| 5   | P1[23]/MCI1/<br>PWM1[4]/MISO0         | 6   | P1[26]/MCOB1/<br>PWM1[6]/CAP0[0] | 7   | P1[27]/CLKOUT<br>/USB_OVRCR/<br>CAP0[1] | 8   | P0[0]/RD1/TXD3/SDA1                   |

| 9   | P0[11]/RXD2/<br>SCL2/MAT3[1]          | 10  | P2[12]/EINT2/<br>I2STX_WS        | 11  | -                                       | 12  | -                                     |

# 6.2 Pin description

Table 4. Pin description

| Symbol            | Pin                 | Ball        | Type          | Description                                                                                                                                                                                                                                        |                                                   |

|-------------------|---------------------|-------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| P0[0] to P0[31]   |                     |             | I/O           | <b>Port 0:</b> Port 0 is a 32-bit I/O port with individual direction controls for each bit. The operation of port 0 pins depends upon the pin function selected via the pin connect block. Pins 12, 13, 14, and 31 of this port are not available. |                                                   |

| P0[0]/RD1/TXD3/   | 46 <sup>[1]</sup>   | K8[1]       | I/O           | P0[0] — General purpose digital input/output pin.                                                                                                                                                                                                  |                                                   |

| SDA1              |                     |             | I             | RD1 — CAN1 receiver input. (LPC1769/68/66/65/64 only).                                                                                                                                                                                             |                                                   |

|                   |                     |             | 0             | TXD3 — Transmitter output for UART3.                                                                                                                                                                                                               |                                                   |

|                   |                     |             | I/O           | <b>SDA1</b> — I <sup>2</sup> C1 data input/output. (This is not an I <sup>2</sup> C-bus compliant open-drain pin).                                                                                                                                 |                                                   |

| P0[1]/TD1/RXD3/   |                     | 7[1] J8[1]  | J8 <u>[1]</u> | I/O                                                                                                                                                                                                                                                | P0[1] — General purpose digital input/output pin. |

| SCL1              |                     |             | 0             | TD1 — CAN1 transmitter output. (LPC1769/68/66/65/64 only).                                                                                                                                                                                         |                                                   |

|                   |                     |             |               | 1                                                                                                                                                                                                                                                  | RXD3 — Receiver input for UART3.                  |

|                   |                     |             | I/O           | <b>SCL1</b> — I <sup>2</sup> C1 clock input/output. (This is not an I <sup>2</sup> C-bus compliant open-drain pin).                                                                                                                                |                                                   |

| P0[2]/TXD0/AD0[7] | 98[2] C4[2]         | 98[2] C4[2] | C4[2]         | I/O                                                                                                                                                                                                                                                | P0[2] — General purpose digital input/output pin. |

|                   |                     |             | 0             | <b>TXD0</b> — Transmitter output for UART0.                                                                                                                                                                                                        |                                                   |

|                   |                     |             | I             | AD0[7] — A/D converter 0, input 7.                                                                                                                                                                                                                 |                                                   |

| P0[3]/RXD0/AD0[6] | 99 <mark>[2]</mark> | A2[2]       | I/O           | P0[3] — General purpose digital input/output pin.                                                                                                                                                                                                  |                                                   |

|                   |                     |             | I             | RXD0 — Receiver input for UART0.                                                                                                                                                                                                                   |                                                   |

|                   |                     |             | 1             | AD0[6] — A/D converter 0, input 6.                                                                                                                                                                                                                 |                                                   |

Table 4. Pin description ...continued

| Symbol                      | Pin                 | Ball            | Type                                           | Description                                                                                                                                                                                    |                                                                                                                                                                                                                  |     |                                                   |  |  |     |

|-----------------------------|---------------------|-----------------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------------------------------|--|--|-----|

| P0[4]/                      | 81 <mark>[1]</mark> | A8[1]           | I/O                                            | P0[4] — General purpose digital input/output pin.                                                                                                                                              |                                                                                                                                                                                                                  |     |                                                   |  |  |     |

| I2SRX_CLK/<br>RD2/CAP2[0]   |                     |                 | I/O                                            | <b>I2SRX_CLK</b> — Receive Clock. It is driven by the master and received by the slave. Corresponds to the signal SCK in the <i>PS-bus</i> specification. (LPC1769/68/67/66/65/63 only).       |                                                                                                                                                                                                                  |     |                                                   |  |  |     |

|                             |                     |                 | I                                              | RD2 — CAN2 receiver input. (LPC1769/68/66/65/64 only).                                                                                                                                         |                                                                                                                                                                                                                  |     |                                                   |  |  |     |

|                             |                     |                 | I                                              | CAP2[0] — Capture input for Timer 2, channel 0.                                                                                                                                                |                                                                                                                                                                                                                  |     |                                                   |  |  |     |

| P0[5]/                      | 80 <u>[1]</u>       | D7[1]           | I/O                                            | P0[5] — General purpose digital input/output pin.                                                                                                                                              |                                                                                                                                                                                                                  |     |                                                   |  |  |     |

| I2SRX_WS/<br>TD2/CAP2[1]    | I                   |                 | I/O                                            | <b>I2SRX_WS</b> — Receive Word Select. It is driven by the master and received by the slave. Corresponds to the signal WS in the $\ell$ S-bus specification. (LPC1769/68/67/66/65/63 only).    |                                                                                                                                                                                                                  |     |                                                   |  |  |     |

|                             |                     |                 | 0                                              | TD2 — CAN2 transmitter output. (LPC1769/68/66/65/64 only).                                                                                                                                     |                                                                                                                                                                                                                  |     |                                                   |  |  |     |

|                             |                     |                 | I                                              | CAP2[1] — Capture input for Timer 2, channel 1.                                                                                                                                                |                                                                                                                                                                                                                  |     |                                                   |  |  |     |

| P0[6]/                      | 79 <mark>[1]</mark> | B8[1]           | I/O                                            | P0[6] — General purpose digital input/output pin.                                                                                                                                              |                                                                                                                                                                                                                  |     |                                                   |  |  |     |

| I2SRX_SDA/<br>SSEL1/MAT2[0] |                     |                 | I/O                                            | <b>I2SRX_SDA</b> — Receive data. It is driven by the transmitter and read by the receiver. Corresponds to the signal SD in the <i>PS-bus</i> specification. (LPC1769/68/67/66/65/63 only).     |                                                                                                                                                                                                                  |     |                                                   |  |  |     |

|                             |                     |                 | I/O                                            | SSEL1 — Slave Select for SSP1.                                                                                                                                                                 |                                                                                                                                                                                                                  |     |                                                   |  |  |     |

|                             |                     |                 | 0                                              | MAT2[0] — Match output for Timer 2, channel 0.                                                                                                                                                 |                                                                                                                                                                                                                  |     |                                                   |  |  |     |

|                             | A9[1]               | l A9[1]         | I/O                                            | P0[7] — General purpose digital input/output pin.                                                                                                                                              |                                                                                                                                                                                                                  |     |                                                   |  |  |     |

| I2STX_CLK/<br>SCK1/MAT2[1]  |                     |                 |                                                |                                                                                                                                                                                                |                                                                                                                                                                                                                  |     |                                                   |  |  | I/O |

|                             |                     |                 | I/O                                            | SCK1 — Serial Clock for SSP1.                                                                                                                                                                  |                                                                                                                                                                                                                  |     |                                                   |  |  |     |

|                             |                     | 0               | MAT2[1] — Match output for Timer 2, channel 1. |                                                                                                                                                                                                |                                                                                                                                                                                                                  |     |                                                   |  |  |     |

| P0[8]/                      | 77[1] C8[1]         | <u>1]</u> C8[1] | 7 <sup>[1]</sup> C8 <sup>[1]</sup>             | C8[1]                                                                                                                                                                                          | C8[1]                                                                                                                                                                                                            | I/O | P0[8] — General purpose digital input/output pin. |  |  |     |

| I2STX_WS/<br>MISO1/MAT2[2]  |                     |                 | I/O                                            | <b>I2STX_WS</b> — Transmit Word Select. It is driven by the master and received by the slave. Corresponds to the signal WS in the <i>PS-bus specification</i> . (LPC1769/68/67/66/65/63 only). |                                                                                                                                                                                                                  |     |                                                   |  |  |     |

|                             |                     |                 | I/O                                            | MISO1 — Master In Slave Out for SSP1.                                                                                                                                                          |                                                                                                                                                                                                                  |     |                                                   |  |  |     |

|                             |                     |                 | 0                                              | MAT2[2] — Match output for Timer 2, channel 2.                                                                                                                                                 |                                                                                                                                                                                                                  |     |                                                   |  |  |     |

| P0[9]/                      | 76 <u>[1]</u>       | A10[1]          | I/O                                            | P0[9] — General purpose digital input/output pin.                                                                                                                                              |                                                                                                                                                                                                                  |     |                                                   |  |  |     |

| I2STX_SDA/<br>MOSI1/MAT2[3] |                     |                 |                                                | I/O                                                                                                                                                                                            | <b>I2STX_SDA</b> — Transmit data. It is driven by the transmitter and read by the receiver. Corresponds to the signal SD in the <i>l</i> <sup>2</sup> <i>S-bus</i> specification. (LPC1769/68/67/66/65/63 only). |     |                                                   |  |  |     |

|                             |                     |                 | I/O                                            | MOSI1 — Master Out Slave In for SSP1.                                                                                                                                                          |                                                                                                                                                                                                                  |     |                                                   |  |  |     |

|                             |                     |                 | 0                                              | MAT2[3] — Match output for Timer 2, channel 3.                                                                                                                                                 |                                                                                                                                                                                                                  |     |                                                   |  |  |     |

| P0[10]/TXD2/                | 48 <mark>[1]</mark> | H7[1]           | I/O                                            | P0[10] — General purpose digital input/output pin.                                                                                                                                             |                                                                                                                                                                                                                  |     |                                                   |  |  |     |

| SDA2/MAT3[0]                |                     |                 | 0                                              | TXD2 — Transmitter output for UART2.                                                                                                                                                           |                                                                                                                                                                                                                  |     |                                                   |  |  |     |

|                             |                     |                 | I/O                                            | SDA2 — I <sup>2</sup> C2 data input/output (this is not an open-drain pin).                                                                                                                    |                                                                                                                                                                                                                  |     |                                                   |  |  |     |

|                             |                     |                 | 0                                              | MAT3[0] — Match output for Timer 3, channel 0.                                                                                                                                                 |                                                                                                                                                                                                                  |     |                                                   |  |  |     |

| P0[11]/RXD2/                | 49 <mark>[1]</mark> | K9[1]           | I/O                                            | P0[11] — General purpose digital input/output pin.                                                                                                                                             |                                                                                                                                                                                                                  |     |                                                   |  |  |     |

| SCL2/MAT3[1]                |                     |                 | I                                              | RXD2 — Receiver input for UART2.                                                                                                                                                               |                                                                                                                                                                                                                  |     |                                                   |  |  |     |

|                             |                     |                 | I/O                                            | SCL2 — I <sup>2</sup> C2 clock input/output (this is not an open-drain pin).                                                                                                                   |                                                                                                                                                                                                                  |     |                                                   |  |  |     |

|                             |                     | 0               | MAT3[1] — Match output for Timer 3, channel 1. |                                                                                                                                                                                                |                                                                                                                                                                                                                  |     |                                                   |  |  |     |

Table 4. Pin description ...continued

| Symbol           | Pin                       | Ball                | Type                                                                                                                                                                                     | Description                                                                                                              |

|------------------|---------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| P0[15]/TXD1/     | 62[1]                     | F10 <sup>[1]</sup>  | I/O                                                                                                                                                                                      | P0[15] — General purpose digital input/output pin.                                                                       |

| SCK0/SCK         |                           |                     | 0                                                                                                                                                                                        | TXD1 — Transmitter output for UART1.                                                                                     |

|                  |                           |                     | I/O                                                                                                                                                                                      | SCK0 — Serial clock for SSP0.                                                                                            |

|                  |                           |                     | I/O                                                                                                                                                                                      | SCK — Serial clock for SPI.                                                                                              |

| P0[16]/RXD1/     | 63 <mark>[1]</mark>       | F8[1]               | I/O                                                                                                                                                                                      | P0[16] — General purpose digital input/output pin.                                                                       |

| SSEL0/SSEL       |                           |                     | I                                                                                                                                                                                        | RXD1 — Receiver input for UART1.                                                                                         |

|                  |                           |                     | I/O                                                                                                                                                                                      | SSEL0 — Slave Select for SSP0.                                                                                           |

|                  |                           |                     | I/O                                                                                                                                                                                      | SSEL — Slave Select for SPI.                                                                                             |

| P0[17]/CTS1/     | 61 <mark>11</mark>        | F9[1]               | I/O                                                                                                                                                                                      | P0[17] — General purpose digital input/output pin.                                                                       |

| MISO0/MISO       |                           |                     | I                                                                                                                                                                                        | CTS1 — Clear to Send input for UART1.                                                                                    |

|                  |                           |                     | I/O                                                                                                                                                                                      | MISO0 — Master In Slave Out for SSP0.                                                                                    |

|                  |                           |                     | I/O                                                                                                                                                                                      | MISO — Master In Slave Out for SPI.                                                                                      |

| P0[18]/DCD1/     | 60 <mark>11</mark>        | F6[1]               | I/O                                                                                                                                                                                      | P0[18] — General purpose digital input/output pin.                                                                       |

| MOSI0/MOSI       |                           |                     | ı                                                                                                                                                                                        | <b>DCD1</b> — Data Carrier Detect input for UART1.                                                                       |

|                  |                           |                     | I/O                                                                                                                                                                                      | MOSI0 — Master Out Slave In for SSP0.                                                                                    |

|                  |                           |                     | I/O                                                                                                                                                                                      | MOSI — Master Out Slave In for SPI.                                                                                      |

| P0[19]/DSR1/     | DSR1/ 59 <sup>[1]</sup> ( | 9[1] G10[1]         | I/O                                                                                                                                                                                      | P0[19] — General purpose digital input/output pin.                                                                       |

| SDA1             |                           |                     | l                                                                                                                                                                                        | <b>DSR1</b> — Data Set Ready input for UART1.                                                                            |

|                  |                           |                     | I/O                                                                                                                                                                                      | <b>SDA1</b> — I <sup>2</sup> C1 data input/output (this is not an I <sup>2</sup> C-bus compliant open-drain pin).        |

| P0[20]/DTR1/SCL1 | 58 <mark>[1]</mark>       | G9[1]               | I/O                                                                                                                                                                                      | P0[20] — General purpose digital input/output pin.                                                                       |

|                  |                           |                     | 0                                                                                                                                                                                        | <b>DTR1</b> — Data Terminal Ready output for UART1. Can also be configured to be an RS-485/EIA-485 output enable signal. |

|                  |                           |                     | I/O                                                                                                                                                                                      | <b>SCL1</b> — I <sup>2</sup> C1 clock input/output (this is not an I <sup>2</sup> C-bus compliant open-drain pin).       |

| P0[21]/RI1/RD1   | 57 <mark>[1]</mark>       | G8 <mark>[1]</mark> | I/O                                                                                                                                                                                      | P0[21] — General purpose digital input/output pin.                                                                       |

|                  |                           |                     | I                                                                                                                                                                                        | RI1 — Ring Indicator input for UART1.                                                                                    |

|                  |                           |                     | I                                                                                                                                                                                        | RD1 — CAN1 receiver input. (LPC1769/68/66/65/64 only).                                                                   |

| P0[22]/RTS1/TD1  | 56 <mark>[1]</mark>       | H10[1]              | I/O                                                                                                                                                                                      | P0[22] — General purpose digital input/output pin.                                                                       |

|                  |                           |                     | 0                                                                                                                                                                                        | RTS1 — Request to Send output for UART1. Can also be configured to be an RS-485/EIA-485 output enable signal.            |

|                  |                           |                     | 0                                                                                                                                                                                        | TD1 — CAN1 transmitter output. (LPC1769/68/66/65/64 only).                                                               |

| P0[23]/AD0[0]/   | 9 <mark>[2]</mark>        | E5[2]               | I/O                                                                                                                                                                                      | P0[23] — General purpose digital input/output pin.                                                                       |

| I2SRX_CLK/       |                           |                     | I                                                                                                                                                                                        | AD0[0] — A/D converter 0, input 0.                                                                                       |

| CAP3[0]          |                           | I/O                 | <b>I2SRX_CLK</b> — Receive Clock. It is driven by the master and received by the slave. Corresponds to the signal SCK in the <i>PS-bus</i> specification. (LPC1769/68/67/66/65/63 only). |                                                                                                                          |

|                  |                           |                     | 1                                                                                                                                                                                        | CAP3[0] — Capture input for Timer 3, channel 0.                                                                          |

Table 4. Pin description ...continued

| Symbol                   | Pin                 | Ball                | Type                       | Description                                                                                                                                                                                                                                                   |                                                                                 |                                                                                 |  |  |

|--------------------------|---------------------|---------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--|--|

| P0[24]/AD0[1]/           | 8 <u>[2]</u>        | D1[2]               | I/O                        | P0[24] — General purpose digital input/output pin.                                                                                                                                                                                                            |                                                                                 |                                                                                 |  |  |

| I2SRX_WS/<br>CAP3[1]     |                     |                     | I                          | AD0[1] — A/D converter 0, input 1.                                                                                                                                                                                                                            |                                                                                 |                                                                                 |  |  |

| CAFS[1]                  |                     |                     | I/O                        | <b>I2SRX_WS</b> — Receive Word Select. It is driven by the master and received by the slave. Corresponds to the signal WS in the <i>PS-bus specification</i> . (LPC1769/68/67/66/65/63 only).                                                                 |                                                                                 |                                                                                 |  |  |

|                          |                     |                     | I                          | CAP3[1] — Capture input for Timer 3, channel 1.                                                                                                                                                                                                               |                                                                                 |                                                                                 |  |  |

| P0[25]/AD0[2]/           | RX_SDA/             | D2[2]               | I/O                        | P0[25] — General purpose digital input/output pin.                                                                                                                                                                                                            |                                                                                 |                                                                                 |  |  |

| I2SRX_SDA/               |                     |                     | I                          | AD0[2] — A/D converter 0, input 2.                                                                                                                                                                                                                            |                                                                                 |                                                                                 |  |  |

| TXD3                     |                     |                     | I/O                        | <b>I2SRX_SDA</b> — Receive data. It is driven by the transmitter and read by the receiver. Corresponds to the signal SD in the $\ell$ S-bus specification. (LPC1769/68/67/66/65).                                                                             |                                                                                 |                                                                                 |  |  |

|                          |                     |                     | 0                          | TXD3 — Transmitter output for UART3.                                                                                                                                                                                                                          |                                                                                 |                                                                                 |  |  |

| P0[26]/AD0[3]/           | 6 <mark>[3]</mark>  | D3[3]               | I/O                        | P0[26] — General purpose digital input/output pin.                                                                                                                                                                                                            |                                                                                 |                                                                                 |  |  |

| AOUT/RXD3                |                     |                     | I                          | AD0[3] — A/D converter 0, input 3.                                                                                                                                                                                                                            |                                                                                 |                                                                                 |  |  |

|                          |                     |                     | 0                          | <b>AOUT</b> — DAC output (LPC1769/68/67/66/65/63 only).                                                                                                                                                                                                       |                                                                                 |                                                                                 |  |  |

|                          |                     |                     | I                          | RXD3 — Receiver input for UART3.                                                                                                                                                                                                                              |                                                                                 |                                                                                 |  |  |

| P0[27]/SDA0/<br>USB_SDA  | 25 <sup>[4]</sup>   | 5[4] J2[4]          | [4] J2[4]                  | I/O                                                                                                                                                                                                                                                           | <b>P0[27]</b> — General purpose digital input/output pin. Output is open-drain. |                                                                                 |  |  |

|                          |                     |                     | I/O                        | <b>SDA0</b> — I <sup>2</sup> C0 data input/output. Open-drain output (for I <sup>2</sup> C-bus compliance).                                                                                                                                                   |                                                                                 |                                                                                 |  |  |

|                          |                     |                     | I/O                        | <b>USB_SDA</b> — USB port I <sup>2</sup> C serial data (OTG transceiver, LPC1769/68/66/65 only).                                                                                                                                                              |                                                                                 |                                                                                 |  |  |

| P0[28]/SCL0/<br>USB_SCL  | 24 <sup>[4]</sup>   | 4[4] J1[4]          | [ <u>4</u> ] J1 <u>[4]</u> | J1 <sup>[4]</sup>                                                                                                                                                                                                                                             | I/O                                                                             | <b>P0[28]</b> — General purpose digital input/output pin. Output is open-drain. |  |  |

|                          |                     |                     |                            |                                                                                                                                                                                                                                                               |                                                                                 |                                                                                 |  |  |

|                          |                     |                     | I/O                        | <b>USB_SCL</b> — USB port I <sup>2</sup> C serial clock (OTG transceiver, LPC1769/68/66/65 only).                                                                                                                                                             |                                                                                 |                                                                                 |  |  |

| P0[29]/USB_D+            | 29 <mark>[5]</mark> | J3 <mark>[5]</mark> | I/O                        | P0[29] — General purpose digital input/output pin.                                                                                                                                                                                                            |                                                                                 |                                                                                 |  |  |

|                          |                     |                     | I/O                        | <b>USB_D+</b> — USB bidirectional D+ line. (LPC1769/68/66/65/64 only).                                                                                                                                                                                        |                                                                                 |                                                                                 |  |  |

| P0[30]/USB_D-            | 30 <mark>[5]</mark> | G4[5]               | I/O                        | P0[30] — General purpose digital input/output pin.                                                                                                                                                                                                            |                                                                                 |                                                                                 |  |  |

|                          |                     |                     | I/O                        | <b>USB_D-</b> — USB bidirectional D- line. (LPC1769/68/66/65/64 only).                                                                                                                                                                                        |                                                                                 |                                                                                 |  |  |

| P1[0] to P1[31]          |                     |                     | I/O                        | <b>Port 1:</b> Port 1 is a 32-bit I/O port with individual direction controls for each bit. The operation of port 1 pins depends upon the pin function selected via the pin connect block. Pins 2, 3, 5, 6, 7, 11, 12, and 13 of this port are not available. |                                                                                 |                                                                                 |  |  |

| P1[0]/                   | 95 <mark>[1]</mark> | D5[1]               | I/O                        | P1[0] — General purpose digital input/output pin.                                                                                                                                                                                                             |                                                                                 |                                                                                 |  |  |

| ENET_TXD0                |                     |                     | 0                          | ENET_TXD0 — Ethernet transmit data 0. (LPC1769/68/67/66/64 only                                                                                                                                                                                               |                                                                                 |                                                                                 |  |  |

| P1[1]/                   | 94 <mark>[1]</mark> | B4[1]               | I/O                        | P1[1] — General purpose digital input/output pin.                                                                                                                                                                                                             |                                                                                 |                                                                                 |  |  |

| ENET_TXD1                |                     |                     | 0                          | ENET_TXD1 — Ethernet transmit data 1. (LPC1769/68/67/66/64 only                                                                                                                                                                                               |                                                                                 |                                                                                 |  |  |

| P1[4]/                   | 93 <mark>[1]</mark> | A4[1]               | I/O                        | P1[4] — General purpose digital input/output pin.                                                                                                                                                                                                             |                                                                                 |                                                                                 |  |  |

| ENET_TX_EN               |                     |                     | 0                          | ENET_TX_EN — Ethernet transmit data enable. (LPC1769/68/67/66/64 only).                                                                                                                                                                                       |                                                                                 |                                                                                 |  |  |

| P1[8]/                   | 92 <mark>[1]</mark> | C5[1]               | I/O                        | P1[8] — General purpose digital input/output pin.                                                                                                                                                                                                             |                                                                                 |                                                                                 |  |  |

| ENET_CRS                 |                     |                     | I                          | ENET_CRS — Ethernet carrier sense. (LPC1769/68/67/66/64 only).                                                                                                                                                                                                |                                                                                 |                                                                                 |  |  |

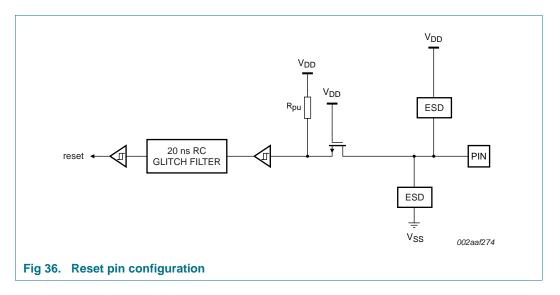

| PC1769_68_67_66_65_64_63 |                     |                     | All information            | provided in this document is subject to legal disclaimers.  © NXP B.V. 2012. All rights reserved.                                                                                                                                                             |                                                                                 |                                                                                 |  |  |