# ATF15XXBE Product Brief

Complex Programmable Logic Devices (CPLDs)

## **Key Features**

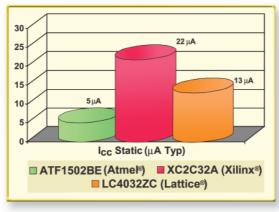

- Ultra-low Standby Current The Industry's Lowest Standby Current (5 μA)

- 1.8-volt Device Operation I/O Voltages Compatible with 1.5V, 1.8V, 2.5V and 3.3V Logic Levels to Simplify Multi-voltage System Design

- A Wide Range of Densities From 32 to 256 Macrocells

- Advanced System Features Multiple I/O Standards, Unique Programming Methods

- Easy In-System Programming (ISP) Support for IEEE® 1532 In-System Programming and IEEE 1149.1 JTAG Boundary Scan Testing

- EEPROM CPLDs Pin-compatible with Industry-standard Devices, Completely Reprogrammable, 10,000 Program/Erase Cycles, 2000V ESD Protection, 200 mA Latch-up Immunity, 100% Tested, 20-year Data Retention

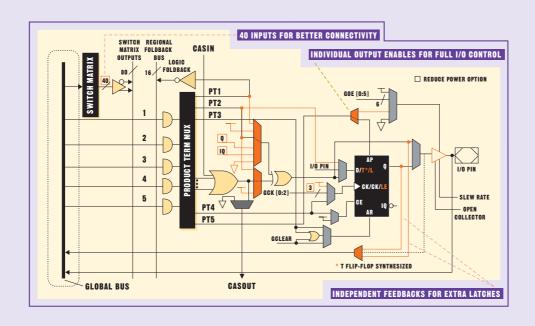

- Logic Doubling® Bury Either Register or COM while Using the Other for Output, Independent Feedback allows Double Latch Functions per Macrocell, 5 Product Terms per Macrocell (Expandable up to 40 Product Terms), Multiple Global and per Macrocell Clocks, Global and/or per Macrocell Output Enable

# ATF150ABE

## **CPLD Product Offering**

| VCC  | Device    | Macrocells | Speed (ns) | Power     | Standby |

|------|-----------|------------|------------|-----------|---------|

| 1.8V | ATF1502BE | 32         | 5/7        | Ultra Low | 5 μΑ    |

|      | ATF1504BE | 64         | 5/7        | Ultra Low | 10 μΑ   |

|      | ATF1508BE | 128        | 7          | Ultra Low | 10 μΑ   |

|      | ATF1516BE | 256        | 7          | Ultra Low | 10 μΑ   |

### **Advanced System Features**

### I/Os Support

- LVTTL and LVCMOS for Standard Chip-to-Chip Interfacing

- SSTL for Standard Chip-to-Memory Interfacing

- Individually-programmable Pin-keeper Option on Inputs and I/Os

- Individually-programmable Schmitt Trigger Option on Inputs and I/Os

- Individually-programmable Input and I/O Pull-up

- 2 Independent I/O Banks

### **Configuration Mode**

- OTF (On-the-Fly) Configuration Mode

- DRA (Direct Reconfiguration Access)

**■ Ultra-low Static Power**

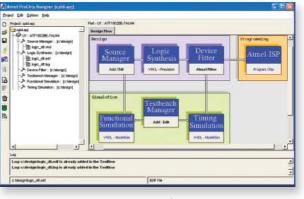

### Software Tools: ProChip Designer Features

- Precision RTL Synthesis VHDL and Verilog<sup>®</sup> Synthesis Supports from Mentor Graphics<sup>®</sup>

- **ModelSim**® VHDL and Verilog Simulation Supports from Mentor Graphics

- FIT15XX Fitters for the ATF15XX CPLDs from Atmel

- HDL Planner VHDL and Verilog Design Entry and Text Editing Supports from Atmel

- Atmel ISP JTAG In-System Programmable (ISP) Support from Atmel

**₹ProChip Designer® Environment**

### **Getting Started**

■ ATF15XX-DK3 CPLD Development Kit – Kickstart your next design by ordering your development kit from one of our Atmel sales representative or distributor. Suggested resale price is \$99. To find a sales representative or distributor in your area, visit our sales contact web page at: <a href="http://www.atmel.com/dyn/general/contact.asp">http://www.atmel.com/dyn/general/contact.asp</a>

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDITIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTIORY WARRANTY RELATIONS OF THE STATUTIORY WARRANTY RELATIONS OF THE STATUTIOR WARRANTY GONE ARTICULAR PURPOSE, OR NON-INFININGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROPTIS, BUSINESSINTERMINITY OF SUCH DAMAGES, Attended to the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided orthorized, or warranted for commitment to update the information contained herein. Unless specifically provided orthorized, or warranted for

# **Headquarters Atmel Corporation**

2325 Orchard Parkway San Jose, CA 95131, **USA** Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

# International

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon, **Hong Kong** Tel: (852) 2721-9778 Fax: (852) 2722-1369

#### Atmel Europe

Le Krebs 8, Rue Jean-Pierre Timbaud BP 309 78054 Saint-Quentin-en-Yvelines Cedex, *France* Tel: (33) 1-30-60-70-00 Fax: (33) 1-30-60-71-11

#### Atmel Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033, Japan

Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

# Product Contact CPLD Programmable Logic

2325 Orchard Parkway San Jose, CA 95131, **USA** Tel: 1(408) 441-0311 Fax: 1(408) 487-2600 www.atmel.com/products/PLD

### **Literature Requests**

www.atmel.com/literature

### Web Site

www.atmel.com

#### © 2007 Atmel Corporation. All rights reserved.

Atmel®, logo and combinations thereof, Everywhere You Are®, Pro-Chip Designer®, Logic Doubling® and others, are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Mentor Graphics®, and ModelSIM® are registered trademarks or trademarks of Mentor Graphics Corporation or its subsidiaries in US and/or other countries. Other terms and product names may be trademarks of the substance of the control of the countries.

3659A-PLD-02/07/5M